Ubung Nr. 8 ¨

Inhaltsverzeichnis

8.1 TTL-Gatter . . . 1

8.2 Gatterschaltungen f¨ur die EXOR-Funktion . . . 3

8.3 Bistabile Kippschaltungen aus TTL-Gattern (S) . . . 3

8.4 MS-Flipflops aus TTL-Gattern . . . 5

8.5 Bin¨arz¨ahler und Untersetzer . . . 6

8.6 Digitale Addition und Subtraktion . . . 6

Achtung:

Bei der Inbetriebnahme von TTL-Bausteinen ist zu beachten, daß der An- schluß V

CCmit +5 V, der Anschluß GND mit Masse zu verbinden ist! Eing¨ ange sollten immer zwischen diesen zwei Grenzspannungen liegen!

8.1 TTL-Gatter

Der Schaltzustand eines TTL-Bausteins l¨aßt sich mit dem Oszilloskop oder der optischen Anzeige nach Abb. 1 darstellen. Der Funktionsgenerator kann mit weniger als 1 Hz betrieben werden. Ist dies zu schnell, wird der Eingangspegel der Schaltungen mit einem Schalter gewechselt bzw. mit Kabeln auf VCC oder GND gesteckt.

470

Abbildung 1: a) Optische Anzeige der Schaltwerte von TTL-Ausg¨angen und b) das von uns verwendete Zeichen

Teil 1: Eingangsstufe Die Arbeitsweise von TTL-Eingangsstufen l¨aßt sich anhand von Abb. 2 in diskretem Aufbau untersuchen. Dabei istT2entbehrlich. Der Basisstrom vonT3ist durch einen Schutz- widerstand (3.3 kΩ) zu begrenzen.

Der Eingangx1 wird offen gelassen (T3 s¨attigt), an +5 V gelegt (T1leitet invers, T3 s¨attigt) oder an Masse gelegt (T1 leitet normal,T3 sperrt). Messen Sie jeweils die SpannungenUB1 undUy um Auskunft uber die jeweiligen Zust¨¨ ande der Transistoren zu bekommen.

T

T x

x

3k3

3k3 1k

5V

y U

T

B1

1

2 1

2

3

Abbildung 2: Prinzipschaltung einer TTL-Eingangsstufe mit diskreten Komponenten

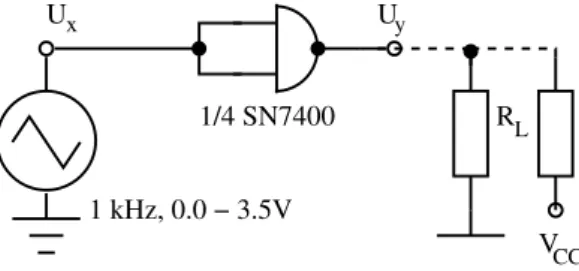

1 kHz, 0.0 − 3.5V

U U

1/4 SN7400 R

V

x y

L

CC

Abbildung 3: Testaufbau zur Ermittlung der statischen Kennlinien von TTL-Gattern (gestrichelt: Die Verschaltung von Lastwiderst¨anden)

Teil 2: ¨Ubertragungskennlinien von TTL-Gattern Die statischen ¨Ubertragungskennlinien von TTL-Gattern werden mit einem Dreiecksgenerator (mit positiven Spannungen!) dargestellt, wobei das Oszilloskop im x-y-Betrieb arbeitet (s.Abb. 3).

Untersuchen Sie zwei Gatter der Bausteine SN74xx00 (NAND), SN74xx02 (NOR), SN7486 (EXOR) oder SN74132 (NAND mit Schmitt-Trigger). Benutzen Sie hierbei Bausteine gleicher Entwicklungsgene- rationen (74 oder 74LS).

Wie ¨andern sich die Kennlinien, wenn jeweils einem Gattereingang ein zeitlich konstanter Schaltwert zugeordnet wird (an Masse, frei oder an +5 V)?

Testen Sie mit verschiedenen Lastwiderst¨anden im Bereich von 2.2 kΩ bis hinunter zu 100Ω zu Mas- se bzw. VCC, wann die Ausgangstreiberf¨ahigkeit des Bausteins nicht mehr ausreicht die zuverl¨assigen Schaltwerte von 0.8 V bzw. 2.0 V zu garantieren.

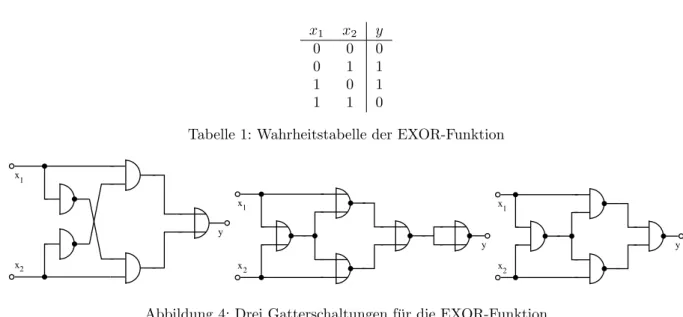

8.2 Gatterschaltungen f¨ ur die EXOR-Funktion

Die ¨Aquivalenz der Schaltungen gem¨aß Abb. 4 kann mit den TTL-Bausteinen SN7400 (NAND, NOT), SN7402 (NOR), SN7408 (AND) und SN7432 (OR)1 nachvollzogen werden. Kontrollieren Sie die Wahr- heitstabelle der EXOR-Funktion Tab. 1 mit allen drei Gatterschaltungen.

1Das OR-Gatter realisiere man im Bedarfsfall aus zwei NOR-Gattern:a+b=a+b.

x1 x2 y

0 0 0

0 1 1

1 0 1

1 1 0

Tabelle 1: Wahrheitstabelle der EXOR-Funktion

x

x

y 1

2

x

x

y 1

2

x

x

y 1

2

Abbildung 4: Drei Gatterschaltungen f¨ur die EXOR-Funktion

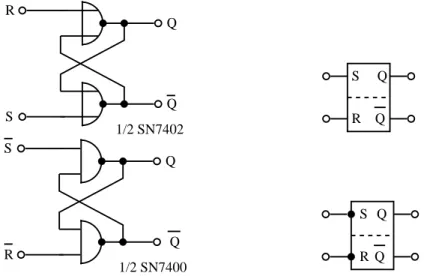

8.3 Bistabile Kippschaltungen aus TTL-Gattern (S)

Teil 1: Bei der Verifizierung der Funktionstabelle 2 der RS-Flipflops in Abb. 5 sind die Eingangs- und Ausgangszust¨ande durch LED’s gem¨aß Abb. 1 anzuzeigen.

Teil 2: Bei dem Betrieb des D-Flipflops in Abb. 6 ist der Eingang D ¨uber einen Widerstand R wechsel- weise mit Masse und mit +5 V zu verbinden. Bei welchem maximalen Wert von R schaltet das Flipflop noch zuverl¨assig?

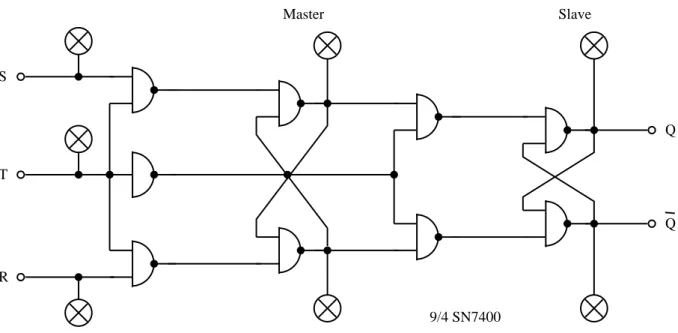

8.4 MS-Flipflops aus TTL-Gattern

Bei den MS-RS-Flipflops in Abb. 7 werden Schaltzust¨ande mit LED’s angezeigt. Der Versuch, den Taktein- gang manuell zu betreiben (Verbinden und L¨osen von T mit bzw. von Masse) muß scheitern, da durch Kontaktprellen die an R und S angelegten Zust¨ande unbeobachtbar schnell auf das Slave-Flipflop ¨ubert- ragen werden. Erst das Vorschalten eines D-Flipflops gem¨aß Abb. 6 vor den Takteingang T erm¨oglicht einen an den LED’s ablesbaren Betrieb.

Teil 1: Die Funktionstabelle 4 ist zu ¨uberpr¨ufen.

Teil 2: Unter Hinzunahme zweier AND-Gatter kann das RS-Flipflop zu einem entsprechenden JK- Flipflop erweitert werden (Abb. 8). Verifizieren Sie Funktionstabelle 5.

S R Q Q

0 0 unver¨andert

0 1 0 1

1 0 1 0

1 1 verboten

Tabelle 2: Funktionstabelle des RS-Flipflops

R

S

Q

1/2 SN7402 Q

Q S R

Q

Q

1/2 SN7400 R

S

Q

Q S R

Q

Abbildung 5: RS-Flipflops aus a) NOR- und b) NAND-Gattern und die zug. Schaltsymbole

D Q Q

0 0 1

1 1 0

Tabelle 3: Funktionstabelle des D-Flipflops

Q

1/2 SN7400 Q D

1

1

1 2

Q D Q

Abbildung 6: D-Flipflop mit Schaltsymbol

S R Qn Qn

0 0 Qn−1 Qn−1

0 1 0 1

1 0 1 0

1 1 verboten

Tabelle 4: Funktionstabelle des MS-RS-Flipflops

S R Qn Qn

0 0 Qn−1 Qn−1

0 1 0 1

1 0 1 0

1 1 Qn−1 Qn−1

Tabelle 5: Funktionstabelle des JK-RS-Flipflops

! " "# $ $%

Master Slave

9/4 SN7400 R

T S

Q

Q

Abbildung 7: Negativ taktzustandsgesteuertes MS-RS-Flipflop mit Diodenanzeige gem¨aß Abb. 1

! !

" "

# #

$ $

% % & &' '

( (

) )

9/4 SN7400

Q

Q J

2/4 SN7408 K

T

Abbildung 8: Negativ taktzustandsgesteuertes JK-RS-Flipflop mit Diodenanzeige gem¨aß Abb. 1

Q

T S

R Q

Q J K

Q T

Abbildung 9: Schaltsymbol f¨ur a) MS-RS-Flipflop und b) JK-RS-Flipflop

J K

B

CLR

J K

C

CLR

J K

D

CLR

J K

A

CLR

Qa Qb Qc Qd

20 21 22 23

R0 R1 INPUT A INPUT B T

SN7493

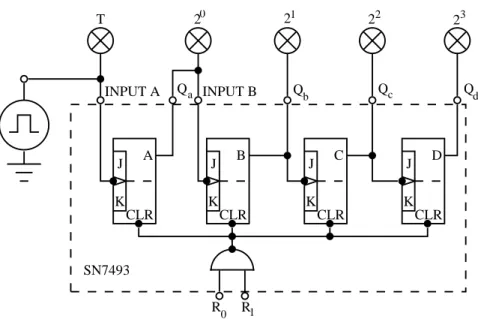

Abbildung 10: Ein integrierter 4-Bit-Bin¨arz¨ahler

a b P

c

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Tabelle 6: Funktionstabelle des Halbaddierers

8.5 Bin¨ arz¨ ahler und Untersetzer

Der Baustein SN7493 in Abb. 10 enth¨alt vier negativ flankengetriggerte MS-JK-Flipflops mit gemeinsamer R¨ucksetzung CLR = R0• R1. Flipflop A kann getrennt betrieben werden, w¨ahrend B bis D intern verbunden sind. Die vorbereitenden Eing¨ange (J,K) liegen auf 1.

Teil 1: Zum Betrieb des 4-Bit-Bin¨arz¨ahlers ist der Funktionsgenerator mit niedrigster Frequenz zu betreiben.

Teil 2: Durch Verbinden der Ausg¨angeQB undQDmit R0 bzw.R1erh¨alt man eine 8241- oder BCD- codierte Dekade und damit auch einen 1:10-Untersetzer. Wie erh¨alt man einen 1:3-, einen 1:9- und einen 1:12-Untersetzer?

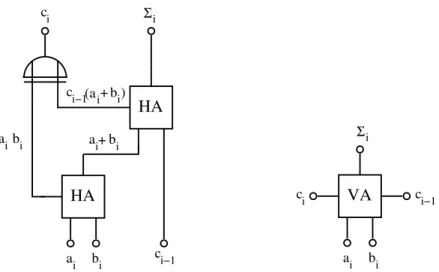

8.6 Digitale Addition und Subtraktion

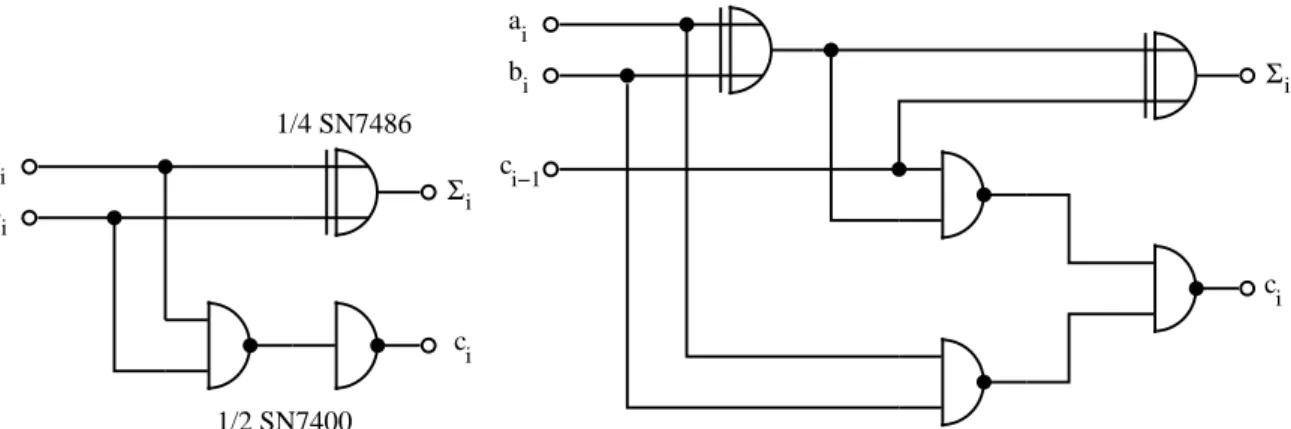

Teil 1: Beim Aufbau und der ¨Uberpr¨ufung der Funktionstabelle 6 des Halbaddierers in Abb. 11 sind ein EXOR-Gatter (1/4 SN7486) und zwei NAND-Gatter (1/2SN7400) (s.Abb. 13a) zu verwenden.

Teil 2: Der Volladdierer in Abb. 12 ber¨ucksichtigt den zus¨atzlichen ¨Ubertragci−1und besteht aus zwei Halbaddierern. Er l¨aßt sich aber einfacher aus zwei EXOR-Gattern (1/2 SN7486) und drei NAND-Gattern (3/4 SN7400) nach Abb. 13b aufbauen.

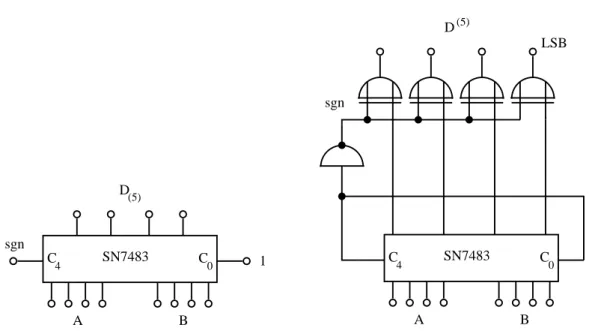

Teil 3: Ein integrierter 4-Bit-Volladdierer SN7483 (Abb. 14) ist in Betrieb zu nehmen und zwei Dual- zahlen in nat¨urlicher Darstellung sind zu addieren.

ai bi

ci Σi

HA

bi

ai

ci

Σi

Abbildung 11: a) Schaltung und b) Symbol des Halbaddierers

ci−1 a b P c

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Tabelle 7: Funktionstabelle des Volladdierers

HA

HA

bi

ai

ci Σi

aib

i

ci−1

ai b + i

(ai b ) + i

ci−1

VA

ci−1bi

ai

Σi

ci

Abbildung 12: a) Aufbau eines Volladdierers aus zwei Halbaddierern und b) Symbol

ai

bi Σi

ci 1/4 SN7486

1/2 SN7400

ai

bi

ci−1

ci

Σi

Abbildung 13: Halb- und Volladdierer mit Einzelgattern

VA VA VA VA

Σ4 Σ3 Σ2 Σ1

c4

c0 c1

c2 c3

B1

A1

A2 B A 2

3 B A 3

4 B

4

C4 C

SN7483 0

B A

LSB

MSB LSB

Σ

MSB

Abbildung 14: a) der 4-Bit-Volladdierer SN7483 und b) symbolische Darstellung

C4 C

0

D(5)

SN7483

B A

1 sgn

C4 C

0

SN7483

B A

LSB

sgn

D(5)

Abbildung 15: Subtrahiernetz zur Bildung von D = B −A in a) der 5-Bit-Darstellung und b) der Standarddarstellung

Teil 4: Bei Betrieb des SN7483 als Subtrahiernetz nach Abb. 15a) sind die Eing¨ange B sowiec4 durch zus¨atzliche NOT’s (z.B. 5/4 SN7400) zu invertieren. Soll die Differenz D = A−B nicht in der 5-Bit- Darstellung,D(5), sondern in der Standarddarstellung,D(5), erscheinen, so ist die Schaltung durch vier EXOR-Gatter (SN7486) zu erg¨anzen (Teilbild b). Wie erzielt man dann die Anzeigen

”+0“ und

”-0“?