Dilyana Dimova Mario Mancino

26. Juli 2004

1 Einführung 1

1.1 Literaturhinweise . . . 1

1.2 Definition: Rechnen . . . 1

1.3 Bool’sche Algebra . . . 1

1.3.1 ∼:{0,1} −→ {0,1} . . . 1

1.3.2 ∧,∨,⊕:{0,1}n−→ {0,1} . . . 1

1.4 Definition: Bool’sche Ausdrücke (vollständig geklammert) . . . 2

1.5 Exkurs: Mengen . . . 2

1.6 Exkurs: Induktionsbeweis . . . 2

1.7 Rechnen mit bool’schen Algebren . . . 2

1.7.1 Definition: Einsetzung . . . 3

1.7.2 Definition:ϕ(e)füre∈BA . . . 3

1.7.3 Definition: Identität (Allgemeingültige Rechenregel) . . . 3

1.7.4 Satz: Kommutativität . . . 4

1.8 Exkurs: Funktionen(6=Funktionssymbole) . . . 4

1.8.1 Definition: Relation . . . 4

1.8.2 Definition: Funktion . . . 5

1.9 Erweiterung zu 1.7.2 . . . 5

1.10 Konventionen . . . 5

1.10.1 Abkürzungen . . . 5

1.11 Definition: elementarer bool’scher Ausdruck . . . 5

1.12 Satz: Darstellungssatz . . . 6

1.12.1 Beweis . . . 6

1.12.2 Beispiel . . . 6

1.13 Lösen einer Gleichung . . . 7

1.13.1 Beispiel 1 . . . 7

1.13.2 Beispiel 2 . . . 7

1.13.3 Beweis:e1∧. . .∧en= 1⇔e1= 1∧. . .∧en= 1 . . . 7

1.13.4 Beweis:e1∨. . .∨en= 1⇔e1= 1∨. . .∨en= 1 . . . 7

1.14 Zusammenhang zwischen Identitäten und Lösungen von Gleichungen . . . 8

1.15 Spezielle bool’sche Ausdrücke . . . 8

1.15.1 Definition: Literal, Monom, Polynom . . . 8

1.15.2 Bemerkung . . . 8

1.15.3 Beispiel . . . 9

1.16 Vollständig disjunktive Normalform . . . 9

1.16.1 Beispiel . . . 9

1.17 Kosten der Darstellungssätze . . . 10

1.17.1 Hilfssätze . . . 10

1.17.2 Kosten . . . 10

1.18 Teure Funktionen . . . 10

1.18.1 Beweis . . . 11

1.18.2 Offene Fragen . . . 11

2 Schaltpläne und Schaltkreise 12 2.1 Gatter . . . 12

2.1.1 Beispiel-Gatter . . . 12

2.1.2 Einsetzung an den Eingängen angelegter Werte . . . 13

2.1.3 Schwierigkeiten von Zyklen . . . 13

2.1.4 Definition: Pfad . . . 14

2.2 Definition: Schaltkreis . . . 14

2.2.1 Hoffnung/Satz . . . 14

2.2.2 Beweis . . . 14

2.3 Satz: Darstellungssatz (Schaltkreise) . . . 15

2.3.1 Definitionen . . . 15

2.3.2 Beweis . . . 15

2.4 Polynome als Schaltkreise . . . 17

2.5 Flache∧/∨Bäume . . . 18

2.5.1 Definition: Schaltkreise∧-n . . . 18

2.5.2 n keine Zweierpotenz . . . 19

2.5.3 Neue Berechnung von Polynomen . . . 20

2.5.4 PLA: Programmed Logic Array . . . 20

3 Zahlendarstellung, Addieren (für ganze Zahlen) 21 3.1 Binärdarstellung . . . 21

3.1.1 Beispiel . . . 21

3.1.2 Größe der Summe . . . 22

3.2 Satz: Eindeutigkeit der Binärdarstellung . . . 22

3.3 Definition: n-bit-Addierer . . . 22

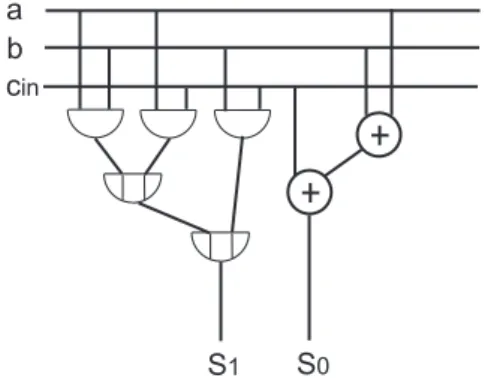

3.4 1-bit Addierer / Volladdierer / Full Adder (FA) . . . 23

3.4.1 Funktionstabelle . . . 23

3.5 Peano Axiome . . . 23

3.6 Zerlegung von Zahlendarstellungen . . . 24

3.7 Additionsalgorithmus . . . 25

3.7.1 Beweis: Induktion über i . . . 25

3.8 Carry-Chain-Adder . . . 26

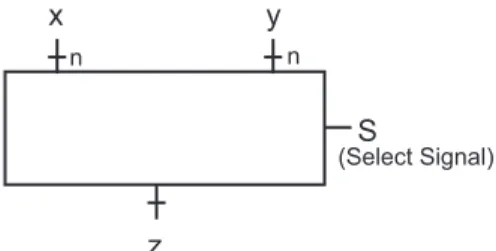

3.9 Definition: Multiplexer (Mux) . . . 27

3.9.1 1-bit Multiplexer Schaltkreis . . . 27

3.9.2 n-Mux . . . 28

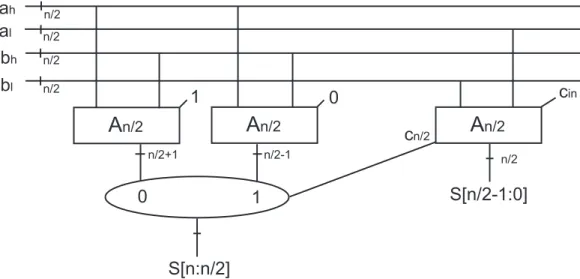

3.10 Conditional Carry Adder . . . 28

3.11 Exkurs: Modulo . . . 29

3.12 Subtraktion . . . 29

3.12.1 Beispiel . . . 29

3.13 Two’s Complement Zahlen . . . 30

3.13.1 Beispiel . . . 30

3.14 Beweis: Subtraktion . . . 30

3.14.1 Lemma 1 . . . 30

3.14.2 Lemma 2 . . . 30

3.14.3 Lemma 3 . . . 31

3.14.4 Lemma 4 . . . 31

3.14.5 Lemma 5 . . . 32

3.14.6 Beweis der Subtraktion . . . 32

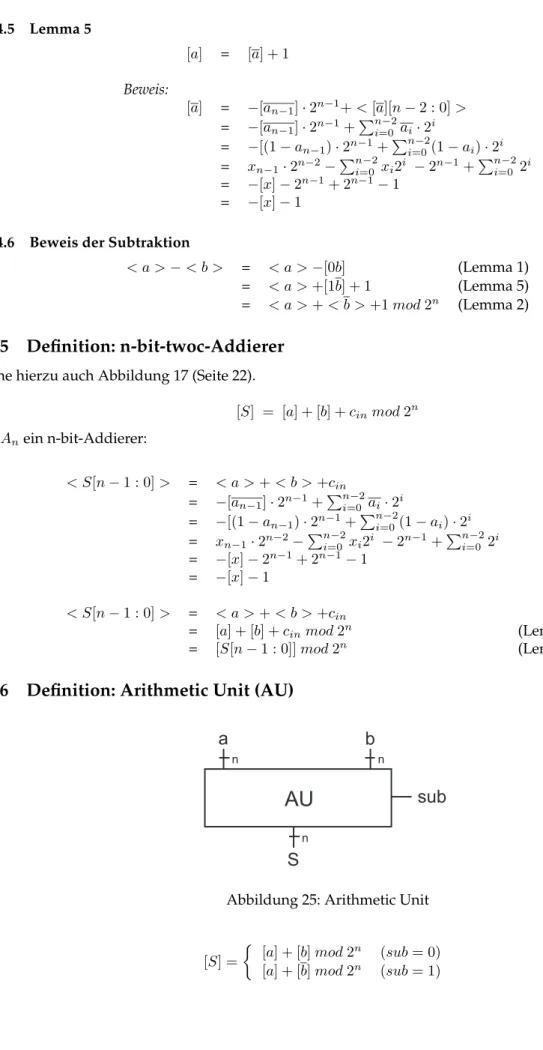

3.15 Definition: n-bit-twoc-Addierer . . . 32

3.16 Definition: Arithmetic Unit (AU) . . . 32

3.16.1 Erweiterung der Notation . . . 33

3.17 n-bit-twoc AU (auch für Binärzahlen) . . . 34

3.17.1 Satz: Overflow . . . 35

3.17.2 Satz: Negation . . . 35

3.18 Definition: Arithmetic Logic Unit (ALU) . . . 35

3.18.1 Steuerbit-Tabelle . . . 36

3.18.2 Schaltkreis . . . 36

3.18.3 akt: Overflow aktivieren/ignorieren . . . 37

3.18.4 xcc: Fixed Point Condition Code . . . 37

4.2 Speicherelemente . . . 39

4.2.1 Register (n-Bit) . . . 39

4.2.2 Random Access Memory (RAM) . . . 40

4.3 Instruktionssatz desDLX0-Prozessors . . . 41

4.3.1 Konfiguration . . . 41

4.3.2 Rechnung . . . 41

4.3.3 3 Instruktionsformate . . . 42

4.3.4 Definition: Signed Extension . . . 43

4.3.5 GP R[05] . . . 43

4.3.6 Instruktionen . . . 43

4.3.7 Zusammenfassung: Instruktionen . . . 45

4.4 Hardware-Konfiguration . . . 45

4.4.1 Unterteilung der Instruktionen in Stufen . . . 46

4.5 Beweis der Gleichheit zwischenDLX0- und Hardware-Konfiguration . . . 47

4.5.1 c0comp . . . 48

4.5.2 adcomp . . . 49

4.5.3 aluoph . . . 50

4.5.4 mw . . . 50

4.5.5 ci.m = hi.m . . . 51

4.5.6 GP R.w . . . 51

4.5.7 P Cinc. . . 52

4.5.8 Spezifikation: n-Inc . . . 52

4.5.9 nextP C . . . 53

5 Compiler fürC0(PASCAL mit C-Syntax) 55 5.1 Kontextfreie Grammatiken . . . 55

5.1.1 Beispiel: Kontextfreie Grammatik . . . 55

5.1.2 Definition: Kontextfreie Grammatik . . . 55

5.1.3 Arbeitsweise von Grammatiken . . . 56

5.1.4 Weitere Definitionen . . . 57

5.1.5 Problem: Alternativer Ableitungsbaum . . . 57

5.1.6 Definition: Eindeutigkeit von Grammatiken . . . 58

5.1.7 Satz: GrammatikGist eindeutig . . . 58

5.2 Aufbohren der Grammatik . . . 58

5.2.1 Bool’sche Ausdrücke . . . 58

5.2.2 Komplexe Datentypen . . . 58

5.2.3 Anweisungen . . . 59

5.2.4 Programm . . . 59

5.2.5 Deklarationen . . . 59

5.3 Semantik vonC0 . . . 60

5.4 Deklarations-Teil . . . 60

5.4.1 Typen-Definition . . . 60

5.4.2 Variablen-Deklaration . . . 63

5.4.3 Funktions-Deklaration . . . 66

5.4.4 Speicher derC0-Maschine . . . 67

5.5 Zusammenfassung der Grammatik . . . 68

5.6 Ausdrucksauswertung . . . 69

5.6.1 Definition: Bindungsfunktion(c, N a → (m, i)) . . . 69

5.6.2 Auswertung . . . 70

5.7 Ausführung von Anweisungen . . . 71

5.8 Compilieren . . . 72

5.8.1 Compiler . . . 72

5.9.1 Definition: Compiler - Korrektheit . . . 78

5.9.2 Definition: abase . . . 78

5.9.3 Beispiel . . . 80

5.9.4 Exkurs: Aho-Ullmann-Algorithmus . . . 80

5.9.5 Satz: Ahu-Ullmann . . . 81

5.9.6 g-Ausdrucksübersetzung . . . 83

5.9.7 r-Konsistenz . . . 88

5.9.8 c-Konsistenz . . . 89

5.9.9 Satz . . . 90

5.9.10 Pre-Order-Traversal . . . 90

5.9.11 Code-Generierung . . . 91

6 Erweiterungen zurDLX0 95 6.1 DLX0mit Interrupts . . . 95

6.1.1 Definition: Interrupt . . . 95

6.1.2 Grober Ablauf . . . 95

6.1.3 Klassifikation . . . 95

6.1.4 Interrupts desDLX0 . . . 96

6.1.5 Konfiguration / Register . . . 97

6.1.6 Definition:δfürDLX0mit Interrupts . . . 97

6.1.7 Neue Instruktionen . . . 98

6.1.8 Interrupts . . . 98

6.1.9 Definition: nicht sichtbar . . . 98

6.1.10 Definition: JISR-Signal (Jump ISR) . . . 98

6.1.11 Definition: Interrupt Level . . . 98

6.1.12 Delta-Funktion . . . 99

6.1.13 Aufbau der ISR . . . 99

6.1.14 Devices & I/O (Geräte & E/A) . . . 100

6.1.15 Beispiel: Hard Disk (HD) . . . 101

6.2 Virtueller Speicher(VM) . . . 102

6.2.1 Motivation . . . 102

6.2.2 Vergleich zweier Maschinen . . . 103

6.2.3 DLX0mit Interrupts & Adress Translation . . . 103

6.2.4 Page Table Lookup . . . 104

6.2.5 Page Fault Exception . . . 104

6.2.6 Instruktionsausführung . . . 105

6.2.7 Simulation . . . 106

6.2.8 Theorem . . . 106

7 Betriebssystem-Kern 107 7.1 CVM: Syntax und Semantik . . . 107

7.1.1 Exkurs: Syntax vonk . . . 108

7.1.2 Semantik voncp . . . 109

7.1.3 Semantik von Interrupts . . . 109

7.1.4 Formalismus zum Spefizieren der Handler von Kernel Calls . . . 110

7.2 CVM mit I/O-Devices . . . 111

7.2.1 Wiederholung: Interrupts . . . 111

7.2.2 return . . . 112

7.2.3 Kernel Calls . . . 112

7.2.4 „User-Functions“ . . . 114

7.2.5 Devices . . . 115

7.3 Definition:C0A(C0mit Assembler-Code) . . . 116

7.4.2 Restriktionen anasm(s) . . . 118

7.4.3 Datenstrukturen des konkreten KernsK . . . 119

7.5 Simulationssatz . . . 121

7.5.1 Definition:konsis(cc, kbase, c) . . . 121

7.5.2 Definition:e−konsis(c, kbase, cc). . . 121

7.5.3 Definition:p−konsis(c, kbase, cc) . . . 122

7.5.4 Definition:c−konsis(c, cc) . . . 122

7.6 Korrekturen . . . 123

7.6.1 Notation:body(. . . , . . .). . . 123

7.7 body(main, k) . . . 124

7.8 body(main, K) . . . 124

7.9 Definition:c−consis(c, cc) . . . 124

7.10 Bootstrap . . . 125

1 Einführung

1.1 Literaturhinweise

• S.M. Müller, W.J. Paul: Computer Architecture (Springer 2000)

• J. Keller, W.J. Paul: Hardware Design (vergriffen)

• G.Even: Skript

1.2 Definition: Rechnen

Rechnen: (Hoffentlich sinnvolle) Manipulation von Zeichenreihen Beispiel: Hardware

Definition: Schaltfunktionf :{0,1}n−→ {0,1}

Ziel: Bauen von Boxen, die Schaltfunktionen berechnen Kalkül: Bool’sche Algebra

Variablen: V ={x0, x1, x2, . . .}

1.3 Bool’sche Algebra

1.3.1 ∼:{0,1} −→ {0,1}

x ∼x

0 1

1 0

1.3.2 ∧,∨,⊕:{0,1}n −→ {0,1}

x0 x1 x0∧x1 x0∨x1 x0⊕x1

0 0 0 0 0

0 1 0 1 1

1 0 0 1 1

1 1 1 1 0

1.4 Definition: Bool’sche Ausdrücke (vollständig geklammert)

1. B0=V ∪ {0,1}

2. e1, e2∈Bi ⇒ e1, e2∈Bi+1

(∼e1)∈Bi+1

e1∧e2∈Bi+1

e1∨e2∈Bi+1

e1⊕e2∈Bi+1

( sonst nichts inBi+1) 3. BA=S∞

i=0Bi

Beispiel:

(x1∧((∼x2)∨x3))∈BA Beweis:

x1, x2, x3∈V ⊆B0, B1, B3, . . . (∼x2)∈B1, B2, . . . ((∼x2)∨x3)∈B2, . . . (x1∧((∼x2)∨x3))∈B3, . . .⊆BA

1.5 Exkurs: Mengen

M: Menge,n∈N

Mn={(a1, . . . , an)|ai∈M} Beispiel:

M ={0,1}

M1={(0),(1)}

M2={(0,0),(0,1),(1,0),(1,1)}

M3={(0,0,0),(0,0,1), . . .}

1.6 Exkurs: Induktionsbeweis

A(n): Aussage 1. Zeige A(1)

2. Zeige A(n)→A(n+1) 3. Schliesse: A(n) für allen∈N

1.7 Rechnen mit bool’schen Algebren

Beispiel:

x1∧x2=x2∧x1

((x1∧x2)∧x3) = (x1∧(x2∧x3))

1.7.1 Definition: Einsetzung ϕ:V → {0,1}

Intuition: setze fürxiWerteϕ(xi)ein.

Beispiel:

ϕ x1 0 x2 1 x3 0 1.7.2 Definition:ϕ(e)füre∈BA

ϕ(0) = 0 ϕ(1) = 1

ϕ(e1∧e2) =ϕ(e1)∧ϕ(e2) ϕ(e1∨e2) =ϕ(e1)∨ϕ(e2) ϕ(e1⊕e2) =ϕ(e1)⊕ϕ(e2)

ϕ(∼e) =∼ϕ(e) Beispiel:

e= (x1∧((∼x2)∨x3)) ϕ(x1) = 0 ϕ(x2) = 1 ϕ(x3) = 0 Einsetzung:

ϕ(∼x2) = ∼ϕ(x2)

= ∼1

= 0

ϕ((∼x2)∨x3) = ϕ(∼x2)∨ϕ(x3)

= 0∨0

= 0

ϕ(e) = ϕ(x1)∧ϕ((∼x2)∨x3)

= 0∧0

= 0

1.7.3 Definition: Identität (Allgemeingültige Rechenregel) e1, e2∈BA:

e1≡e2⇔ϕ(e1) =ϕ(e2)fur alle ϕ¨

1.7.4 Satz: Kommutativität

x1∧x2=x2∧x1

x1∨x2=x2∨x1

x1⊕x2=x2⊕x1

Beweis: trivial durch Ausprobieren aller Fälle.

Rechenregeln:

(x1∧x2)∧x3=x1∧(x2∧x3) x1∧(x2∨x3) = (x1∧x2)∨(x1∧x3)

1.8 Exkurs: Funktionen(6=Funktionssymbole)

Seien X,Y Mengen, dann gilt:

X×Y ={(x, y)|x∈X, y∈Y} Beispiel:

{0,1}2 = {0,1} × {0,1}

{0,1}3 6= {0,1} × {0,1}2 {0,1}3 = {(0,0,0),(0,0,1), . . .}

{0,1} × {0,1}2 = {(0,(0,0)),(0,(0,1)), . . .}

1.8.1 Definition: Relation R⊂X×Y: Relation

z.B.:X =Y =R, R={(x, y)|x≥y}

R

Abbildung 1: Relation

1.8.2 Definition: Funktion

Die Funktion ist eine spezielle (Rechtseindeutige) Relation:

(x, y1)∈R (x, y2)∈R

⇒ y1=y2

Der Funktion liegt eine Funktionstabelle zugrunde,fiist nur ein Name dafür.

1.9 Erweiterung zu 1.7.2

ϕ(f(e1, . . . , es)) =Def f(ϕ(e1), . . . , ϕ(es)))

1.10 Konventionen

Um Schreibarbeit zu sparen, vereinbart man:

∼bindet stärker als∧

∧bindet stärker als∨

1.10.1 Abkürzungen

¯

eist Abkürzung für(∼e) /eist Abkürzung für(∼e) xixjist Abkürzung fürxi∧xj

=ist Abkürzung für≡

x[n: 1]ist Abkürzung für(xn, . . . , x1)

1.11 Definition: elementarer bool’scher Ausdruck

Ein elementarer bool’scher Ausdruck, in dem∧,∨,∼verwendet werden.

ElBA={e∈BA|e elementar}=alte Def inition

1.12 Satz: Darstellungssatz

∀f : {0,1}n→ {0,1} ∃e elem. B.A. mit: e≡f(x1, . . . , xn)

1.12.1 Beweis

Beweis per Induktion über n:

n=0:

f :{0,1}0

| {z }

φ

→ {0,1}

⊆φ× {0,1}

Konvention: 0,1:{0,1}0→ {0,1}

n=1:

Funktionstabelle:

x1 f1 f2 f3 f4

0 0 1 1 0

1 0 1 0 1

e 0 1 x1 x1

n→n+1:

f(x1, . . . , xn+1) =xn+1∧f(x1, . . . , xn,1)∨xn+1∧f(x1, . . . , xn,0) 1.12.2 Beispiel

x1 x2 x3 f(x3, x2, x1) f(0, x2, x1) f(0,0, x1)

0 0 0 0 0 0

0 0 1 1 1 1

z}|{x1

f(0,1, x1)

0 1 0 1 1 1

0 1 1 0 0 0

z }| {

e0=x2x1∨x2x1

z}|{x1

f(1, x2, x1) f(1,0, x1)

1 0 0 1 1 1

1 0 1 1 1 1

z}|{1 f(1,1, x1)

1 1 0 1 1 1

1 1 1 0 0 0

z }| {

e0=x2∧1∨x2x1

z}|{x1

1.13 Lösen einer Gleichung

Einsetzung mitϕ(e) =ϕ(e′)heißtLösender Gleichung.

1.13.1 Beispiel 1

Sei e ein elementarer bool’scher Ausdruck.

e= 1 Lösung: Einsetzen vonϕmit:

ϕ(e) =ϕ(1) = 1 ϕ(e) =∼ϕ(e) = 1⇔ϕ(e) = 0 d.h. ϕLösung vone= 1

⇔ ϕLösung vone= 0 Dies wird abgekürzt alse= 1⇔e= 0

1.13.2 Beispiel 2

Seien e, e’ elementare bool’sche Ausdrücke.

e∧e’ = 1 SeiϕLösung:

ϕ(e∧e′) =ϕ(1) = 1 ϕ(e)∧ϕ(e′)⇔ϕ(e) = 1∧ϕ(e′) = 1

⇔ ϕLösung von e=1

und ϕLösung von e’=1 1.13.3 Beweis:e1∧. . .∧en= 1⇔e1= 1∧. . .∧en= 1

Induktion über n:

n=2:

e1=e e2=e′ (eben in 1.13.1 und 1.13.2 gemacht)n→n+1:

e1∧. . .∧en−1

| {z }

e

∧ en

|{z}

e′

= 1⇔e1∧. . .∧en−1= 1

| {z }

⇔e1=1∧...∧en−1=1

und en= 1

1.13.4 Beweis:e1∨. . .∨en= 1⇔e1= 1∨. . .∨en= 1 Der Beweis läuft analog zu 1.13.3.

1.14 Zusammenhang zwischen Identitäten und Lösungen von Gleichungen

Seien e, e’ elementare bool’sche Ausdrücke.

L¨osung von e=1, e′=1

z }| {

∀ϕ: ϕLösung vone= 1

⇔ ϕLösung vone′= 1 ϕ(e) = 1 ⇔ ϕ(e′) = 1 ϕ(e) = 0 ⇔ ϕ(e′) = 0

| {z }

e≡e′

Um e≡e’ zu zeigen, genügt es zu zeigen:

Gleichung e=1 und e’=1 haben gleiche Lösungen - Kurz:

e=1⇔e’=1

e≡e’ ⇔

e=1⇔e’=1

1.15 Spezielle bool’sche Ausdrücke

1.15.1 Definition: Literal, Monom, Polynom Seienx1, x2, . . . , xnVariablen.

Ausdruck L heißtLiteral:

⇔L=xifür einxi

Ausdruck M heißtM onom:

⇔M =L1∧. . .∧Lsfür einsund LiteraleLi. . . Ls

Ausdruck P heißtP olynom:

⇔P =M1∨. . .∨Ltfür eintund MonomeMi. . . Ms

1.15.2 Bemerkung Gleichungen

L= 1 M = 1

P = 1 können wir lösen.

Notation:

ǫ∈ {0,1}

xǫi =

½ xi:ǫ= 1 xi:ǫ= 0 xǫi = 1⇔xi=ǫ

1.15.3 Beispiel

Seia=a[n: 1]∈ {0,1}n,a7→M(a) =Def.xann∧. . .∧xa11

| {z }

(M onom)

n=3, a=101:

M(a) = x13∧x02∧x11

= x3x2x1

M(a) = 1 ⇔ xaii = 1f¨ur alle i

⇔ xi=aifur alle i¨

⇔ x[n: 1] =a[n: 1]

M(a) = 1⇔x=a

1.16 Vollständig disjunktive Normalform

Seif :{0,1}n→ {0,1}

T(f) ={a∈ {0,1}n|f(a) = 1}

| {z }

(T r¨ager von f)

T(f)7→P(f) = _

a∈T(f)

M(a) (P olynom)

| {z }

(V ollst¨andig disjunktive N ormalf orm von f)

P(f) = 1 ⇔ es gibt a∈T(f) : M(a) = 1

⇔ es gibt a∈T(f) : x=a

⇔ x∈T(f)

⇒ P(f)≡f

(Neuer Beweis des Darstellungssatzes) 1.16.1 Beispiel

x3 x2 x1 f(x)

0 0 0 1

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 0

1 1 1 1

T(f)={ 000 , 011 , 100 , 101 , 111 }

↓ ↓ ↓ ↓ ↓

M(000) M(011) M(100) M(101) M(111)

= = = = =

x3x2x1 x3x2x1 x3x2x1 x3x2x1 x3x2x1 ≡ f(x3, x2, x1)

1.17 Kosten der Darstellungssätze

C(e) = Anzahl Vorkommen von∧,∨,∼in e (Kosten)

G(e) = größte auftretende Kosten für einf :{0,1}n → {0,1}

1.17.1 Hilfssätze

#M = Anzahl der Elemente in M (Mächtigkeit von M)

#(M ×N) = #M ·#N

#(MN) = (#M)N ⇒ #{0,1}n= (#{o,1}n = 2n 1.17.2 Kosten

1. f(x)≡W

a∈Tm(a)

vollständige disjunktive Normalform, Kosten:

G(f)≤2n·2n 2. f(x[n: 1]) =xn·f(1, x[n−1 : 1])∨xn·f(0, x[n−1 : 1])

Differenzengleichung:

G(1) = 1

G(n) = 4 + 2· · · G(n-1) geraten (k=n-1):

G(n) = 2k· · ·G(n−k) + 2k+1+ 2k+. . .+ 4

= 2n−1· · ·G(1) + 2n+ 2n−1+. . .+ 4 + (+2 + 1

| {z }

2n+1−1

−3)

= 2n+1+ 2n−1−4

= 5. . .2n−1−4

1.18 Teure Funktionen

Gibt esf :{0,1}n → {0,1}für das gilt: Jedese, dasf berechnet ist teuer?

Ja:

• Jedeseberechnet eine Funktion

• Die Menge der billigen Ausdrücke ist klein

⇒ {f|∃:ebillig undeberechnetf}ist klein,{f : [0,1]n→ {0,1}}ist groß

1.18.1 Beweis

Seieein elementarer bool’scher Ausdruck.

A={x1, . . . , xn,(,),∧,∨,∼, ,0,1}

#A=n+ 8

22n = #{f|f :{0,1}n→ {0,1}}

≤ #{e|G(e)≤k}

= #(A5k

= (n+ 8)5k

k: ∀f :{0,1}n → {0,1} ∃e: e≡f(x) G(e)≤k

k≥ 2n

5·log(n+ 8)

1.18.2 Offene Fragen

• Wie sehenf aus, für die jedeseteuer ist?

⊕erlauben?

A={x1, . . . , xn,(,),∧,∨,∼, ,0,1,⊕}

#A=n+ 9

k≥ 2n

5·log(n+ 9)

• Bool’sches Polynom p:

Hat die Gleichung p=0 eine Lösung?

Gibt es einschnellesRechenverfahren?

P = NP?

2 Schaltpläne und Schaltkreise

2.1 Gatter

Eingänge: x1 x2

Gatter: Box zur Berechnung von Schaltfunktionen Ausgänge: y1. . . yn(Kabel, Leitungen)

Å ~

. ,

-Gatter

, .

-GatterÅ

-Gatter InverterAbbildung 2: Gatter-Symbole

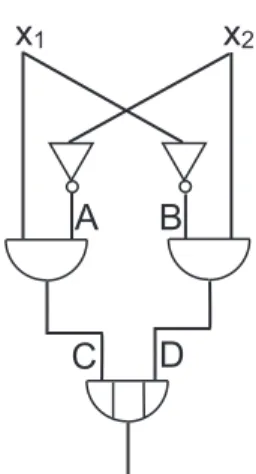

2.1.1 Beispiel-Gatter

x

2A B

C D x

1Abbildung 3: Schaltkreis - XOR Gatter

x1 x2 A B C D E

0 0 1 1 0 0 0

0 1 0 1 0 1 1

1 0 1 0 1 0 1

1 1 0 0 0 0 0

G≡x1⊕x2

2.1.2 Einsetzung an den Eingängen angelegter Werte

ϕ:{x1, . . . , xn} → {0,1}

Z’, Z”: Eingänge des Gatters in Schaltung S Z: Ausgang eines Gatters in Schaltung S

f: berechnete Funktion des Gatters in Schaltung S

Abbildung 4: Eingänge des Gatters

ϕ(Z) = f(ϕ(Z′), ϕ(Z′′))

=

ϕ(Z′)∧ϕ(Z′′) : f =∧ ϕ(Z′)∨ϕ(Z′′) : f =∨ ϕ(Z′)⊕ϕ(Z′′) : f =⊕ ϕ(Z) = ∼ϕ(Z′)

2.1.3 Schwierigkeiten von Zyklen

1

Abbildung 5: Schaltkreis - Zyklen-Problem

ϕ(A) = 1⇒ϕ(B) = 0⇒ϕ(A) = 0!

ϕ(A) = 0⇒ϕ(B) = 1⇒ϕ(A) = 1!

Abbildung 6: Schaltkreis - AND Flip-Flop

Bei beiden Beispielen ergeben sich Probleme, da in den jeweiligen Gattern mit den Untergattern G1, . . . , GSvon einem UntergatterGnzu einem vorherigen GatterGn−k(0< k < n)gesprungen wird.

2.1.4 Definition: Pfad Der Pfad wird definiert durch:

G1→G2→. . .→GS

Dabei ist S die Länge das Pfades.

2.2 Definition: Schaltkreis

Ein Schaltkreis ist eine Schaltung in der keine Zyklen vorkommen dürfen.

2.2.1 Hoffnung/Satz

Wir hoffen ein Schaltkreis ist für alleZ mitZ =EingangoderZ =Ausgangeines Gattersϕ(Z)wohldefi- niert.

2.2.2 Beweis

Induktion über die Tiefe zwischen Z und den Eingängen.

Die Tiefe von einem Gatter ist die Länge eines längsten Pfades von den Eingängen zu G:

Abbildung 7: Tiefe (Formal)

T ief e(G) =max{T ief e(G′), T ief e(G′′)}+ 1 2.2.3 Beispiel

x

21

x

11

2 2

3

Abbildung 8: Schaltkreis - XOR-Gatters (Tiefe)

T ief e(G) =max{T ief e(G′), T ief e(G′′)}+ 1

2.2.4 Hilfssatz

In einem Schaltkreis hat jedes Gatter eine Tiefe.

Beweis:

Annahme: GatterGin SchaltkreisShat keine Tiefe:

d.h.: ∀t∃Pfad von den Eingängen zuGmit Länger≥t x1→G1→. . .→Gt→G

SeiSendlich,E=#GatterinS, t > E

⇒ Gatter wiederholt sich⇒Zyklus!

Um zu beweisen, dassϕwohldefiniert ist, bedient man sich einer Induktion über die Tiefe(G).

2.3 Satz: Darstellungssatz (Schaltkreise)

∀f : {0,1}n→ {0,1} ∃Schaltkreis S: S berechnet f 2.3.1 Definitionen

S berechnet f, f alls∃Leitung u in S: u ≡ f(x1, . . . , xn)

K(S) = #Gatter von S (Kosten)

T(S) = max{T ief e(G)|G ist Gatter in S}

2.3.2 Beweis

Seiebool’scher Ausdruck.

Behauptung:

∃SchaltkreisS

∃LeitunguinS:u ≡ e Induktion über i:

e∈BAi

e∈BA0

e∈ {0,1, x1, . . . , xi}

0,1 erlauben wir als Eingänge von jedem Schaltkreis:

i→i+1:

◦ ∈ {∧,∨,⊕}

e′, e′′ ∈ BAi

1. e=e′◦e′′

x[1:n]

n Bus der Breite n

Abkürzung für:

x1

xn

S(e') S(e'')

u

Abbildung 9: Schaltkreise - Darstellungssatz (Binäre Operationen)

2. e=∼e′

x[1:n]

n

S(e')

u

Abbildung 10: Schaltkreise - Darstellungssatz (Negation)

Bemerkung: K(S(e)) = G(e)

2.4 Polynome als Schaltkreise

Sei e Polynom:

e = M1∧. . .∧Mt

Mi = Li1∧. . .∧Mij

Mik = {x1, . . . , xn, x1, . . . , xn} Zur Berechnung aller Literale reichen n Inverter.

x

1_

x

1x

n_

x

nVe r b i n d e m i t L e i t u n g e n Li j d i e z u M o n o m Mi

g e h ö r e n

M

1M

2M

2M

tAbbildung 11: Schaltkreise - Polynom

T ief e leq 1 + max{j, i}+t−2 leq 1 + +n+ 2n−2

langsam!

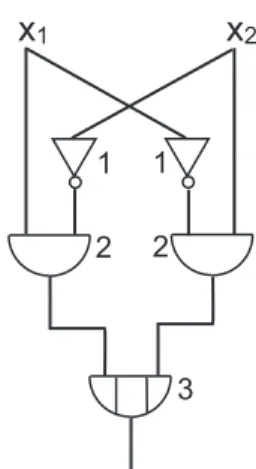

2.5 Flache ∧ / ∨ Bäume

2.5.1 Definition: Schaltkreise∧-n n=1:

x0

T(∧1) = 0

n=2:

x

0x

1Abbildung 12: Schaltkreise -∧ −2Baum T(∧2) = 1

n 2 →n:

x [ n - 1 : n / 2 ] x [ n / 2 - 1 : 0 ]

n / 2 n / 2

Abbildung 13: Schaltkreise -∧ −nBaum T(∧n) = T(∧n/2) + 1 = log2n

Es giltu ≡ vwegen Assoziativität von∧.

n

x

0x

n-1n

u v

Abbildung 14: Vergleich -∧−Reihe /∧ −nBaum

2.5.2 n keine Zweierpotenz Falls n keine Zweierpotenz ist:

n = n′+k n

2 ≤ n′

= max{2i|2i≤n}

k = n−n′

≤ n 2 In diesem Fall sieht∧nso aus:

n' k

Abbildung 15: Schaltkreise -∧ −nBaum, falls n keine Zweierpotenz ist

2.5.3 Neue Berechnung von Polynomen

Tiefe≤

x1 _

x1

xn _

xn 1

+

j(i) ⌈log2n⌉

+

t

M

1M

iM

t⌈log2n⌉

t≤2n≤n+ log2n+ 2 2.5.4 PLA: Programmed Logic Array

Verwendung zur Realisierung sogenannter „random logic“:

Es werden keine Regelmäßigkeiten der Funktionstabelle ausgenutzt (Zufall = Abwesenheit von Regelmä- ßigkeiten)

3 Zahlendarstellung, Addieren (für ganze Zahlen)

a[n-1:0] b[n-1:0]

n n

Abbildung 16: Addierer Kodierung der Eingänge?

Addierer-Schaltkreis?

Kodierung der Summe?

3.1 Binärdarstellung

Binärdarstellungen:

a∈ {0,1}n = {0,1} ∨ {0,1}2∨. . . Dargestellte Zahl:

a∈ {0,1}n

a = a[n−1 : 0] = an−1. . . a0

Definition:

< a >= Pn−1 i=0 ai·2i

⇒

< a > =

n−1X

i=0

ai·2i

≤

n−1X

i=0

2i

= 2n−1

3.1.1 Beispiel

<101> = 1·22+ 0·21+ 1·20

= 4 + 0 + 1

= 5

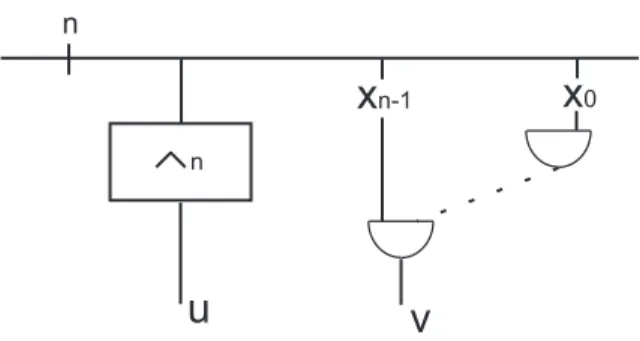

3.1.2 Größe der Summe

SeiS = C0+C1+. . .+Cn−1 (C= 2):

S·C = C1+. . .+Cn−1+Cn S·(C−1) = Cn−C0

= Cn−1 S = Cn−1 C−1

= 2n−1(f alls c= 2)

⇒< a >+< b > ≤ (2n−1)·2

< 2n+1−1

Hoffnung:

∃S ∈ {0,1}n+1 mit < S >=< a >+< b >

3.2 Satz: Eindeutigkeit der Binärdarstellung

< >: {0,1} → {0, . . . ,2n−1}ist bijektiv (Beweis: Übungsblatt, Hinweis:∨-Baum→ ∨-Gatter-Platzierung) D.h. jede Zahl aus{0, . . . ,2n−1}hat eine eindeutige Binärdarstellung der Längen.

3.3 Definition: n-bit-Addierer

Schaltkreis:

a[n-1:0] b[n-1:0]

n n

n+1

S[n:0]

cin 1

Abbildung 17: n-bit Addierer mit:

< s >=< a > + < b > +cin

3.4 1-bit Addierer / Volladdierer / Full Adder (FA)

cin

b a

S1 S0

Abbildung 18: Schaltkreis - 1-bit Addierer

3.4.1 Funktionstabelle

a b cin S1 S0

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

3.5 Peano Axiome

N achf olgerf unktion N :N0→N0 0 ∈ N0

0 ist eine (natürliche) Zahl.

∀x∈N0∃ <∈ N0: y = N(x) Jede natürliche Zahl hat einen Nachfolger.

¬ ∃y: 0 =N(j)

0 ist nicht Nachfolger einer Zahl.

x6=y ⇔ N(x)6=N(y)

Sind zwei natürliche Zahlen verschieden dann haben sie verschiedene Nachfolger, d.h ausx6=yfolgt x+ 16=y+ 1.

Definition:

N(x) = x+ 1 N(0) = 1 N(1) = 2 N(N(N(0))) = 2·1 + 1

= N(N(0)) +N(0)

= (1 + 1) + 1

Defintion· x . . .0 = 0 x·(y+ 1) = x·y+x x·(0 + 1) = x|{z}·0

0

+x

Defintion+ =

x·1 = x (1 + 1) ˙1 = 1+1

3.6 Zerlegung von Zahlendarstellungen

a ∈ {0, . . . , B−1}n(z.B. B= 10)

< a >B =

n−1X

i=0

aiBi

<101>10 = 1·102+ 0·101+ 1·100

= (1 + 1) + 1

= 101????

Konvention:

Ziffernfolge∈ {0, . . . ,9}- Standardinterpretation:a = a10

a = an−1·. . .·ak·ak−1·. . .·a0

< a[n−1 : 0]>B = < a[n−1 :k]>B ·Bk+< a[k−1 : 0]>B

B= 10, k= 3:

24197 = 24·103+ 197

3.7 Additionsalgorithmus

Summanden:

a = a[n−1 : 0] ∈ {0,1}n b = b[n−1 : 0] ∈ {0,1}n c = c−1

(c1= 1) (c0= 1) (cin= 0) c

1 0 1 a

1 1 1 b

1 1 0 0 S

ci: Übertrag von Stelle i nach Stelle i+1

c−1 = cin

< c1, Si> = ai + bi + ci+1

Sn = cn−1

Satz:

∀i < a[i: 0]> + < b[i: 0]> +cin =< ci, S[i: 0]>

3.7.1 Beweis: Induktion über i i= 0:

< a0>+< b0>+cin = a0+b0

| {z }

Def.:< >

+ c−1

|{z}

Def.:cin

= < c0, S0>

| {z }

Def.:<c0,S0>

c = c−1

i−1→i:

< a[i: 0]>+< b[i: 0]>+cin = ai·2i+< a[i−1 : 0]>+bi·2i+< b[i−1 : 0]>

| {z }

Zerlegung

+cin

= ai·2i+bi·2i + < ci−1, S[i−1 : 0]>

| {z }

Induktionsvorraussetzung

= ai·2i+bi·2i + ci−1·2i+< S[i−1 : 0]>

| {z }

Zerlegung n=k=i

= (ai+bi+ci−1)·2i

| {z }

Distributivgesetzt

+ < S[i−1 : 0]>

= < ci, si>·2i

| {z }

Def.:Additionsschritt

+ < S[i−1 : 0]>

= < ci, si, S[i−1 : 0]>

| {z }

Zerlegung n=i+1, k=i

= < ci, S[i: 0]>

3.8 Carry-Chain-Adder

cin

b0

a0

c0

b0

a0

c1

bn-1

an-1

Sn Sn-1

S1

S0

FA

FA

FA

Abbildung 19: Carry-Chain-Adder

Kosten= n·K(F A) Tiefe≤ n·T(F A) Für alle n-bit Addierer:

Tiefe≥log(2n)

3.9 Definition: Multiplexer (Mux)

n

x y

z

n

S

(Select Signal)

Abbildung 20: Multiplexer

z=

½ x : S= 0 y : S= 1 3.9.1 1-bit Multiplexer Schaltkreis

x y

z

S

Abbildung 21: 1-bit Multiplexer Schaltkreis

z = xs∧ys

3.9.2 n-Mux

y0

x0

yn-1

xn-1

z0

zn-1

S

1 - M u x 1 - M u x

Abbildung 22: n-bit Multiplexer

x y

n

z

0 1 S

n

Abbildung 23: Multiplexer Symbol

3.10 Conditional Carry Adder

Definition von SchaltkreisAn(A1=F A):

a

ha

lb

hb

ln/2 n/2

n/2 n/2

A

n/2A

n/2A

n/21 0

n/2+1 n/2-1 n/2

c

n/2S[n:n/2]

c

inS[n/2-1:0]

1 0

Abbildung 24: Conditional Carry Adder

Tiefe:

T(A1) = T(F A)

T(An) = T(An/2) +T(M ux)

| {z }

3

⇒ T(An) = O(logn)

3.11 Exkurs: Modulo

(u mod v = Rest bei Division durch v ∈ {0, . . . , v−1}

u ≡ u′mod v ⇔ (u mod v) = (u′mod v) Division mit Rest bei u < 0?

u=a·v+b; a∈Z, b∈ {0, . . . , v−1}

3.12 Subtraktion

Notation:

x[n−: 0]

x= (xn−1, . . . , x0) Subtraktionsalgorithmus:x, y ∈ {0,1}n

< x >−< y >= (< x >+< y >+1)mod2n 3.12.1 Beispiel

n=4:

1 1 0 1 1 1 0 1

- 0 1 1 0 Regel→ + 1 0 0 1

+ 1

1 0 1 1 1

mod2

0 1 1 1

3.13 Two’s Complement Zahlen

x ∈ {0,1}n Definition:

[x] = −xn−1·2n−1+< x[n−2 : 0]>

[x]heißt two’s complement Darstellung vonxder Längen

Tn = {−2n−1, . . . ,2n−1−1}

[ ] : 0,1n →Tn

−2n−1 ≤ [x] ≤ hx[n−2 : 0]i ≤ 2n−1−1 3.13.1 Beispiel

[1011] = −1·23+<11>

= −8 + 3

= −5

3.14 Beweis: Subtraktion

Eigenschaften:

a = a[n−1 : 0] ∈ {0,1}n 3.14.1 Lemma 1

< a > = [0a]

Beweis:

[0a] = −0·2n+< a > (Def initionvon[ ])

= < a >

3.14.2 Lemma 2

[a] = < a[n−2 : 0]> mod2n−1 Beweis:

[a] = −an−1·2n−1+< a[n−2 : 0]>

= < a[n−2 : 0]> mod2n−1

3.14.3 Lemma 3

[a] = < a > mod2n Beweis:

[a]−< a > = −an−1·2n−1+< a[n−1 : 0]>−(an−1·2n−1−< a[n−1 : 0]>)

= −2·an−1·2n−1

= 0mod2n Sind Adressen in Rechnern:

• Binärzahlen?

• Two’s Complement Zahlen=

Nach Lemma 3: egal, damod232

3.14.4 Lemma 4

[an−1a] = [a] (Sign Extension)

Beweis:

[an−1a] = −an−1·2n+< a >

= −an−1·2n+an−1·2n−1+< a[n−2 : 0]>

= −an−1·2n−1+< a[n−2 : 0]>

= [a]

Beispiel:

[1011] = [11011]

= [111011]

Definition:

a ∈ {0,1}ninterpretiert als two’s complement Zahl:

an−1: sign-bit

3.14.5 Lemma 5

[a] = [a] + 1 Beweis:

[a] = −[an−1]·2n−1+<[a][n−2 : 0]>

= −[an−1]·2n−1+Pn−2 i=0 ai·2i

= −[(1−an−1)·2n−1+Pn−2

i=0(1−ai)·2i

= xn−1·2n−2−Pn−2

i=0 xi2i −2n−1+Pn−2 i=0 2i

= −[x]−2n−1+ 2n−1−1

= −[x]−1 3.14.6 Beweis der Subtraktion

< a >−< b > = < a >−[0b] (Lemma 1)

= < a >+[1b] + 1 (Lemma 5)

= < a >+< b >+1mod2n (Lemma 2)

3.15 Definition: n-bit-twoc-Addierer

Siehe hierzu auch Abbildung 17 (Seite 22).

[S] = [a] + [b] +cinmod2n SeiAnein n-bit-Addierer:

< S[n−1 : 0]> = < a >+< b >+cin

= −[an−1]·2n−1+Pn−2 i=0 ai·2i

= −[(1−an−1)·2n−1+Pn−2

i=0(1−ai)·2i

= xn−1·2n−2−Pn−2

i=0 xi2i −2n−1+Pn−2 i=0 2i

= −[x]−2n−1+ 2n−1−1

= −[x]−1

< S[n−1 : 0]> = < a >+< b >+cin

= [a] + [b] +cinmod2n (Lemma 3)

= [S[n−1 : 0]]mod2n (Lemma 3)

3.16 Definition: Arithmetic Unit (AU)

a b

S

n n

n

AU sub

Abbildung 25: Arithmetic Unit

[S] =

½ [a] + [b]mod2n (sub= 0) [a] + [b]mod2n (sub= 1)

Nach Lemma 5:

[S] =

½ [a] + [b] + 0mod2n (sub= 0) [a] + [b] + 1mod2n (sub= 1) 3.16.1 Erweiterung der Notation

a ∈ {0,1}n; x ∈ {0,1}

◦: {0,1}n→ {0,1}

a◦x = (an−1◦x, . . . , a0◦x) x◦a = (x◦an−1, . . . , x◦a0)

a b

n 1

n

b b

a

n-1a

0Abk. für:

Abbildung 26: Erweiterung der Notation Beispiel:

b sub

n 1

Abbildung 27: Beispiel: Erweiterung der Notation

b⊕sub = (bn−1⊕sub, . . . , b0⊕sub)

=

½ b (sub= 0) b (sub= 1)

3.17 n-bit-twoc AU (auch für Binärzahlen)

[S] = [a] + [b⊕sub] +sub mod2n

a

b

S[n-1:0]

n n

n

sub

AU

n

neg ovf

Abbildung 28: n-bit-twoc AU (auch für Binärzahlen) Behauptung:

addiert/subtrahiert auch Binärzahlen Frage:

Wann ist[a] + [b] +cin ∈ Tn={−2n−1, . . . ,2n−1−1}?

Definition:

ovf(a, b, cin) ⇔ [a] + [b] +cin ∈/ Tn(overf low) neg(a, b, cin) ⇔ [a] + [b] +cin < 0

3.17.1 Satz: Overflow

ovf(a, b, cin) = 1 ⇔ cn−1+cn−2

3.17.1.1 Beweis

[a] + [b] +cin = −an−1·2n−1−bn−1·2n−1+< a[n−2 : 0]>+< b[n−2 : 0]>

= −an−1·2n−1−bn−1·2n−1+< cn−2, S[n−2 : 0]>

| {z }

=2n−1·cn−2+<S[n−2:0]>

(Korrektheitsbeweis d. Addierers, Induktion bei i=n−2)

= −2n−1(an−1+bn−1+cn−1−2cn−2)+< S[n−2 : 0]>

= −2n−1( < cn−1, Sn−1>

| {z }

2·(cn−1+Sn−1−2cn−2)

+< S[n−2 : 0]>

= −2n(cn−1−cn−2) + [S[n−1 : 0]]

= δ

Fallcn−1=cn−2:

⇒ δ= [S[n−1 : 0]] ∈ Tn

Fallcn−1= 1; cn−2= 0:

⇒ δ=−2n+ [S]≤ −2n+ 2n−1−1 ∈/ Tn

Fallcn−1= 0; cn−2= 1 ≡ Fallcn−1= 1; cn−2= 0

3.17.2 Satz: Negation

neg(a, b, cin) = 1 ⇔ [a] + [b] +cin < 0 ∈ Tn+1\Tn

neg= an−1⊕bn−1⊕cn−1

3.18 Definition: Arithmetic Logic Unit (ALU)

a b

S[n-1:0]

n n

n

f [3:0]

(Steuerbits)

ALU

4

ovf

Abbildung 29: Arithmetic Logic Unit

3.18.1 Steuerbit-Tabelle

f[3 : 0] S overflow akt./ign.

0 0 0 0 a +n b akt.

0 0 0 1 a +n b ign.

0 0 1 0 a −n b akt.

0 0 1 1 a −n b ign.

0 1 0 0 a ∧ b

0 1 0 1 a ∨ b

0 1 1 0 a ⊕ b

0 1 1 1 b[n/2 : 0] 0n/2

f[3 : 0] xcc(1, b, f) ≡

< = >

1 0 0 0 0

1 0 0 1 a > b a−b > 0

1 0 1 0 a = b a−b = 0

1 0 1 1 a ≥ b a−b ≥ 0

1 1 0 0 a < b a−b < 0

1 1 0 1 a 6= b a−b 6= 0

1 1 1 0 a 6= b a−b 6= 0

1 1 1 1 1

3.18.2 Schaltkreis

a n

b n

n-AU

neg akt* ovf'

ovf

Interrupt Unit

sub f[1]

f[3]

b[n/2-1:0] 0n/2

0 1 0 1

f[0] f[0]

0 1

f[1]

n n n

0 1

0 1

f[2]

f[3]

0n-1 xcc*

S''

S'

S

n

n

n

n

null*

Abbildung 30: Schaltkreis - Arithmetic Logic Unit

3.18.3 akt: Overflow aktivieren/ignorieren

akt = f3f2f0

3.18.4 xcc: Fixed Point Condition Code

neg(a, b, f) = 1 ⇔ a−b < 1 null(a, b, f) = 1 ⇔ a−b = 1 pos(a, b, f) = 1 ⇔ a−b > 1

pos = neg∧null

xcc(a, b, f) = f2neg∨f1null∨f0pos

4 Prozessorbau

Prozessor: rechnet in Schritten

Hardware: rechnetbesserauch in Schritten 1. Mathematische Maschinen

2. Register, RAM, multiport-RAM’S (Hardware-Erweiterungen) 3. DLX0: vereinfachter DLX-Instruktionssatz (DLX≈MIPS) 4. Bau vonDLX0-Prozessor

4.1 Mathematische Maschinen

Aus Programmier-Sprachen x := x+ 1

| {z }

nicht Gleichheit!

Definition vonxt: xvor/während Schrittt

→ xt+1 = xt+ 1

x: Register, RAM,. . .: Hardware

x: für Benutzer sichtbare Register : Assembler-Programmierung x: Variablen eines Programms : Programmier-Sprachen

x: für Benutzer sichtbare Datenstrukturen : Betriebssystem

Definition: mathematische Maschinen

M = (τ, δ, c0)

τ : M enge von Konf igurationen

(Zustand d. M aschine in einem Schritt) δ : τ→τ

( ¨U bergangsf unktion) c0 ∈ τ : Startkonf iguration

Rechnung:

F olge(C0, c1, c2, . . .) : ci+i=f(ci)∀i

4.2 Speicherelemente

4.2.1 Register (n-Bit)

Ce

R

Rin n

n

Rout

Abbildung 31: Register

R ∈ {0,1}n (in Register gesp. bits) ce ∈ {0,1} (clock enable) Arbeitsweise:

R := Rinf alls ce= 1

R =

½ Rtin : cte= 1 Rt : sonst Beispiel:

1

n-Add

a n

n 0

n

0 1 0

n

reset

R

1Abbildung 32: Register (Beispiel)

reset0 = 1 resett

| {z }

(t>0)

= 0

R0in = 0n R1in = 0n

Rtin = Rt +n 1n

|{z}

1n=binn(1)

Rt+1 = Rt +n 1

Lemma:

Rt = binn(t) 4.2.2 Random Access Memory (RAM)

S

Din d

d

Dout a

1

ad w

Abbildung 33:2a× dRAM 4.2.2.1 2a× dRAM

S: {0,1}a→ {0,1}d st+1(x) =

½ Dtin : x=adt∧wt= 1 St(x) : sonst

Dtout =St(adt) (f alls wt= 0) Allgemeine Regeln zur Wohldefiniertheit: S.M. Müller, W. Paul:

The Complexity of Simple Computer Architectures, Springer 1995.

S

Din d

d

Dout A

a 1

ad A w

ad B a

ad C a

d

Dout B Abbildung 34:3−P ortRAM 4.2.2.2 3−P ortRAM

S: {0,1}a→ {0,1}d St+1(x) =

½ DinCt : x=adCt∧wt= 1 St(x) : sonst

DoutAt = St(adAt) : (adA6=adC∧wt= 1)∨wt= 0 DoutBt = St(adBt) : (adB6=adC∧wt= 1)∨wt= 0

4.3 Instruktionssatz des DLX

0-Prozessors

m

32

ad 32

CPU

PC

GPR

Abbildung 35:DLX0Instruktionssatz Central Processing Unit:

Memory: Wort-Adressiert Adressen∈ {0,1}32 m: {0,1}32→ {0,1}32

mt(ad) :Inhalt von Speicherzelleadzur Zeitt Program Counter (PC)∈ {0,1}32

General Purpose Register File (GPR):{0,1}5→ {0,1}32 32 Adressen

32 Register

GPR[i]∈ {0,1}32; i ∈ {0,1}5 4.3.1 Konfiguration

c = (c.P C, c.GP R, c.m) c.P C ∈ {0,1}32

c.GP R : {0,1}5→ {0,1}32 c.m : {0,1}32→ {0,1}32

4.3.2 Rechnung Rechnung:(c0, c1, c2, . . .)

ci+1 = δ(ci) Ii= diei-te ausgeführte Instruktion

c0→I0 c1→I1 c2. . . ci I→i ci+1 I(ct) = ct.m[ct.P C] ∈ {0,1}32

N otation: I(ct) ≡ It

Itwird meistens auch im Instruction Register (IR) zwischengespeichert. Effekt von It formal spezifiziert durch:

ct+1 = (ct+1.P C, ct+1.GP R, ct+1.m) = δ(ct)

4.3.3 3 Instruktionsformate I-Type:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OPC RS1 RD imm

R-Type:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OPC RS1 RS2 RD (SA) fu

J-Type:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OPC imm

Der Typ der Instruktion wird im OpCode festgelegt:

opc(c)

| {z }

c=DLX0−Konf iguration

= I(c)[31 : 26]

Prädikate:

R−T ype(c) ⇔ opc(c) = 06

J−T ype(c) ⇔ opc(c) ∈ {000010,000011,111110,111111}

I−T ype(c) ⇔ /(R−T ype(c)∨J−T ype(c))

Felder definieren:

RS1(c) = I(c)[25 : 21]

RS2(c) = I(c)[20 : 16]

RD(c) =

½ I(c)[20 : 16] : I-Type(c) I(c)[15 : 11] sonst f u1(c) = I(c)[5 : 0]

imm(c) =

½ I(c)[15 : 0] : I-Type(c) I(c)[25 : 0] sonst

4.3.4 Definition: Signed Extension Seia ∈ {0,1}b(interpretiert als twoc):

sxt(a) = a[b−1]cb−1a ∈ {0,1}b+c

Lemma:

[imm] = [sxt(imm)]

4.3.5 GP R[05]

Für das GPR desDLX0soll immer gelten:

c.GP R[00000] = 032 4.3.6 Instruktionen

4.3.6.1 Load/Store load word (lw):

lw(c) = 1 ⇔ op(c) = 100011 effective address:

ea(c) = c.GP R[RS1(c)

| {z }

{0,1}5

]

| {z }

{0,1}32

+32sxt2(imm(c)

| {z }

{0,1}16

)

ct+1.GP R[RD(ct)] = ct.m[ea(ct)]

store word (sw):

sw(c) = 1 ⇔ op(c) = 101011

ct+1.m[x] =

½ ct.m[ea(ct)] : sw(c)∧x=ea(ct) ct.m[x] : sonst

2sxt: signed Extension

4.3.6.2 Compute / Compute Immediate compute immedate (comp.imm:)

comp.imm(c) = 1 ⇔ I(c)[31 : 30] = 01

Vergleiche hierzu Kapitel 3.18. Wir benötigen hierzu eine 32-bit ALU.

ct+1.GP R[x] =

½ aluop(c.GP R[RS1(c)], sxt(imm(c)), I(c)[29 : 26]) : x=RD(c)∧x6= 05

ct.GP R[x] : sonst

compute (comp):

comp(c) = 1 ⇔ R−T ype ∧ I(c)[5 : 4] = 00 ct+1.GP R[x] =

½ aluop(c.GP R[RS1(c)], c.GP R[RS2(c)], I(c)[3 : 0]) : x=RD(c)∧x6= 05

ct.GP R[x] : sonst

Zusammenfassung:

lop = c.GP R[RS1(c)]

rop=

½ sxt(imm(c)) : comp.imm(c) c.GP R[RS2(c)] : sonst

lop=

½ I(c)[29 : 26] : comp.imm(c) I(c)[3 : 0] : sonst

4.3.6.3 Branch or Jump taken

bjtaken(c) = 1 ⇔ btaken(c)∧jump(c) branch(c) = 1 ⇔ I(c)[31 : 27] = 11010 AeqZ(c) = 1 ⇔ c.GP R[RS1(c)] = 0

jump(c) = j(c) ∧ jal(c) ∧ jr(c) ∧ jalr(c) beqz(c) = branch(c) ∧ I(c)[26] = 0 bnez(c) = branch(c) ∧ I(c)[26] = 1

btaken(c) = c.GP R[RS1(c)] = 0 ∧ beqz(c) ∨ c.GP R[RS1(c)]6= 0 ∧ bnez(c)

| {z }

Def inition

= branch(c) ∧ [c.GP R[RS1(c)] = 0 ∧ I[26] = 0 ∨ c.GP R[RS1(c)]6= 0 ∧ I[26] = 1)]

⇒Lemma:

btaken(c) = branch(c)∧(AeqZ(c)⊕I[26]) ct+1.P C=

ct.P C(ct) +32 sxt(imm(ct)) : btaken(ct)∧j(ct)∧jal(ct)*

ct.GP R[RS1(ct)] : jr(ct)∧jalr(ct) c.P C(ct) +32 132 : sonst

*Achtung:

imm(c) ∈ {0,1}16oder{0,1}26 sxt(imm) =

½ imm[15]16imm : imm(c) ∈ {0,1}16 imm[25]6imm : imm(c) ∈ {0,1}26

ct+1.GP R[x] =

032 : x= 05

ct.m[ct] : lw(ct) ∧ x=RD(ct) ∧ x6= 05

aluop(lop(ct), rop(ct), f code(ct)) : (comp.imm(ct) ∨ comp(ct)) ∧ x=RD(ct) c.P C +32 132

| {z }

R¨ucksprungadresse

: (jal(ct) ∨ jalr(ct)) ∧ x= 15

ct.GP R[x] : sonst

4.3.7 Zusammenfassung: Instruktionen ct+1.m[x] =

½ ct.m[ea(ct)] : sw(c)∧x=ea(ct) ct.m[x] : sonst

ct+1.P C=

ct.P C(ct) +32 sxt(imm(ct)) : btaken(ct)∧j(ct)∧jal(ct)*

ct.GP R[RS1(ct)] : jr(ct)∧jalr(ct) c.P C(ct) +32 132 : sonst

ct+1.GP R[x] =

032 : x= 05

ct.m[ct] : lw(ct) ∧ x=RD(ct) ∧ x6= 05

aluop(lop(ct), rop(ct), f code(ct)) : (comp.imm(ct) ∨ comp(ct)) ∧ x=RD(ct) c.P C +32 132

| {z }

R¨ucksprungadresse

: (jal(ct) ∨ jalr(ct)) ∧ x= 15

ct.GP R[x] : sonst

4.4 Hardware-Konfiguration

h = (h.P C, h.GP R| {z }

modif iziertes3−P ort RAM

, h.m)