Hochschule Karlsruhe w University of Applied Sciences w Fakultät für Informatik

Prof. Dr. Dirk W. Hoffmann

Kapitel 5

!

Standardschaltnetze

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Inhalt und Lernziele

§ Inhalt

§ Vorstellung der wichtigsten Standardelemente

§ Nur kombinatorische Logik, kein Gedächtnis

§ Multiplexer

§ Demultiplexer

§ PALs, PLAs

§ Halbaddierer, Volladdierer

§ Carry-Ripple-Addierer

§ Carry-Look-Ahead-Addierer

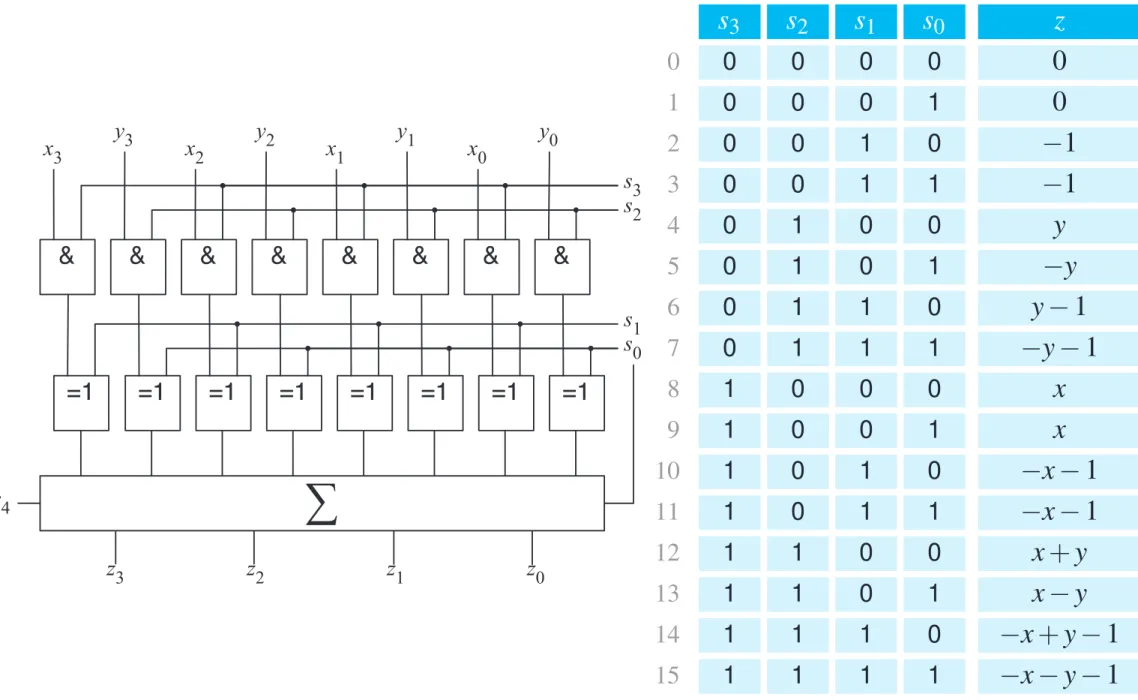

§ ALU

§ Lernziele

§ Kenntnis über Aufbau und Funktion der Schaltelemente

2

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Multiplexer

3

s0 x1

x2

2:1

MUX y

s0 s1 x1

x3 x2

x4 4:1

MUX y

s2 s0 x1

x3 x5 x7 x2 x4 x6 x8

8:1

MUX y

s1

x1

s2 s1 s0 x2

x3 x4 x5 x6 x7 x8

≥1

y

&

&

&

&

&

&

&

&

Abbildung 7.6:Realisierung eines 1-aus-8- Multiplexers mit Hilfe der elementaren Lo- gikgatter

208 7 Standardschaltnetze

s0 x1

x2

2:1

MUX y

s0 s1 x1

x3 x2

x4 4:1

MUX y

s2 s0 x1

x3 x5 x7 x2 x4 x6 x8

8:1

MUX y

s1

s0 y

0 x1

1 x2

s1 s0 y

0 0 x1

0 1 x2

1 0 x3

1 1 x4

s2 s1 s0 y s2 s1 s0 y

0 0 0 x1 1 0 0 x5

0 0 1 x2 1 0 1 x6

0 1 0 x3 1 1 0 x7

0 1 1 x4 1 1 1 x8

Abbildung 7.5: Multiplexer-Bausteine verschiedener Größen

gang y durch. Alle anderen Eingänge werden durch den Multiplexer faktisch vom Rest der Schaltung abgetrennt, so dass die dort anliegen- den Signalwerte für den Ausgangswert keine Rolle spielen. Da mit m Steuerleitungen 2m verschiedene Möglichkeiten unterschieden werden können, entspricht die Anzahl der Eingänge eines Multiplexers in aller Regel einer Zweierpotenz. Abbildung 7.5 fasst die Wahrheitstabellen und Schaltsymbole von Multiplexern verschiedener Größe zusammen.

An dieser Stelle wollen wir uns der Frage zuwenden, wie sich ein Multiplexer-Baustein mit Hilfe der elementaren Logikgatter implemen- tieren lässt. Hierzu überführen wir die Wahrheitstabelle des 1-aus-8- Multiplexers in einen booleschen Ausdruck und erhalten das folgende Ergebnis:

y = (s2 ^s1^s0^x1)_(s2 ^s1 ^s0 ^x2) _ (s2 ^s1^s0^x3)_(s2 ^s1 ^s0 ^x4) _ (s2 ^s1^s0^x5)_(s2 ^s1 ^s0 ^x6) _ (s2 ^s1^s0^x7)_(s2 ^s1 ^s0 ^x8)

Das hieraus resultierende Schaltnetz ist in Abbildung 7.6 dargestellt.

Wie das Strukturbild bereits vermuten lässt, ist der Flächenbedarf großer Multiplexer-Bausteine nicht unerheblich. Implementieren wir die Schaltung, wie hier gezeigt, als zweistufiges Schaltnetz, so benö- tigen wir zur Umsetzung eines 1-aus-n-Multiplexers n UND-Gatter mit jeweils log2n+1 Eingängen. Gehen wir davon aus, dass die Größe ei- nes UND-Gatters proportional mit der Anzahl seiner Eingänge steigt,

x1

s2 s1 s0 x2

x3 x4 x5 x6 x7 x8

≥1

y

&

&

&

&

&

&

&

&

Abbildung 7.6: Realisierung eines 1-aus-8- Multiplexers mit Hilfe der elementaren Lo- gikgatter

208 7 Standardschaltnetze

s0 x1

x2

2:1

MUX y

s0 s1 x1

x3 x2

x4 4:1

MUX y

s2 s0 x1

x3 x5 x7 x2 x4 x6 x8

8:1

MUX y

s1

s0 y

0 x1

1 x2

s1 s0 y

0 0 x1

0 1 x2

1 0 x3

1 1 x4

s2 s1 s0 y s2 s1 s0 y

0 0 0 x1 1 0 0 x5

0 0 1 x2 1 0 1 x6

0 1 0 x3 1 1 0 x7

0 1 1 x4 1 1 1 x8

Abbildung 7.5: Multiplexer-Bausteine verschiedener Größen

gang y durch. Alle anderen Eingänge werden durch den Multiplexer faktisch vom Rest der Schaltung abgetrennt, so dass die dort anliegen- den Signalwerte für den Ausgangswert keine Rolle spielen. Da mit m Steuerleitungen 2m verschiedene Möglichkeiten unterschieden werden können, entspricht die Anzahl der Eingänge eines Multiplexers in aller Regel einer Zweierpotenz. Abbildung 7.5 fasst die Wahrheitstabellen und Schaltsymbole von Multiplexern verschiedener Größe zusammen.

An dieser Stelle wollen wir uns der Frage zuwenden, wie sich ein Multiplexer-Baustein mit Hilfe der elementaren Logikgatter implemen- tieren lässt. Hierzu überführen wir die Wahrheitstabelle des 1-aus-8- Multiplexers in einen booleschen Ausdruck und erhalten das folgende Ergebnis:

y = (s2^s1^s0^x1)_(s2^s1 ^s0^x2) _ (s2^s1^s0^x3)_(s2^s1 ^s0^x4) _ (s2^s1^s0^x5)_(s2^s1 ^s0^x6) _ (s2^s1^s0^x7)_(s2^s1 ^s0^x8)

Das hieraus resultierende Schaltnetz ist in Abbildung 7.6 dargestellt.

Wie das Strukturbild bereits vermuten lässt, ist der Flächenbedarf großer Multiplexer-Bausteine nicht unerheblich. Implementieren wir die Schaltung, wie hier gezeigt, als zweistufiges Schaltnetz, so benö- tigen wir zur Umsetzung eines 1-aus-n-Multiplexers n UND-Gatter mit jeweils log2n+1 Eingängen. Gehen wir davon aus, dass die Größe ei- nes UND-Gatters proportional mit der Anzahl seiner Eingänge steigt,

x1

s2 s1 s0 x2

x3 x4 x5 x6 x7 x8

≥1

y

&

&

&

&

&

&

&

&

Abbildung 7.6: Realisierung eines 1-aus-8- Multiplexers mit Hilfe der elementaren Lo- gikgatter

208 7 Standardschaltnetze

s0 x1

x2

2:1

MUX y

s0 s1 x1

x3 x2

x4 4:1

MUX y

s2 s0 x1

x3 x5 x7 x2 x4 x6 x8

8:1

MUX y

s1

s0 y

0 x1

1 x2

s1 s0 y

0 0 x1

0 1 x2

1 0 x3

1 1 x4

s2 s1 s0 y s2 s1 s0 y

0 0 0 x1 1 0 0 x5

0 0 1 x2 1 0 1 x6

0 1 0 x3 1 1 0 x7

0 1 1 x4 1 1 1 x8

Abbildung 7.5: Multiplexer-Bausteine verschiedener Größen

gang y durch. Alle anderen Eingänge werden durch den Multiplexer faktisch vom Rest der Schaltung abgetrennt, so dass die dort anliegen- den Signalwerte für den Ausgangswert keine Rolle spielen. Da mit m Steuerleitungen 2m verschiedene Möglichkeiten unterschieden werden können, entspricht die Anzahl der Eingänge eines Multiplexers in aller Regel einer Zweierpotenz. Abbildung 7.5 fasst die Wahrheitstabellen und Schaltsymbole von Multiplexern verschiedener Größe zusammen.

An dieser Stelle wollen wir uns der Frage zuwenden, wie sich ein Multiplexer-Baustein mit Hilfe der elementaren Logikgatter implemen- tieren lässt. Hierzu überführen wir die Wahrheitstabelle des 1-aus-8- Multiplexers in einen booleschen Ausdruck und erhalten das folgende Ergebnis:

y = (s2^s1^s0 ^x1)_(s2^s1^s0 ^x2) _ (s2^s1^s0 ^x3)_(s2^s1^s0 ^x4) _ (s2^s1^s0 ^x5)_(s2^s1^s0 ^x6) _ (s2^s1^s0 ^x7)_(s2^s1^s0 ^x8)

Das hieraus resultierende Schaltnetz ist in Abbildung 7.6 dargestellt.

Wie das Strukturbild bereits vermuten lässt, ist der Flächenbedarf großer Multiplexer-Bausteine nicht unerheblich. Implementieren wir die Schaltung, wie hier gezeigt, als zweistufiges Schaltnetz, so benö- tigen wir zur Umsetzung eines 1-aus-n-Multiplexers n UND-Gatter mit jeweils log2n+1 Eingängen. Gehen wir davon aus, dass die Größe ei- nes UND-Gatters proportional mit der Anzahl seiner Eingänge steigt,

x1

s2 s1 s0 x2

x3 x4 x5 x6 x7 x8

≥1

y

&

&

&

&

&

&

&

&

Abbildung 7.6:Realisierung eines 1-aus-8- Multiplexers mit Hilfe der elementaren Lo- gikgatter

208 7 Standardschaltnetze

s0 x1

x2

2:1

MUX y

s0 s1 x1

x3 x2

x4 4:1

MUX y

s2 s0 x1

x3 x5 x7 x2 x4 x6 x8

8:1

MUX y

s1

s0 y

0 x1

1 x2

s1 s0 y

0 0 x1

0 1 x2

1 0 x3

1 1 x4

s2 s1 s0 y s2 s1 s0 y

0 0 0 x1 1 0 0 x5

0 0 1 x2 1 0 1 x6

0 1 0 x3 1 1 0 x7

0 1 1 x4 1 1 1 x8

Abbildung 7.5: Multiplexer-Bausteine verschiedener Größen

gang y durch. Alle anderen Eingänge werden durch den Multiplexer faktisch vom Rest der Schaltung abgetrennt, so dass die dort anliegen- den Signalwerte für den Ausgangswert keine Rolle spielen. Da mit m Steuerleitungen 2m verschiedene Möglichkeiten unterschieden werden können, entspricht die Anzahl der Eingänge eines Multiplexers in aller Regel einer Zweierpotenz. Abbildung 7.5 fasst die Wahrheitstabellen und Schaltsymbole von Multiplexern verschiedener Größe zusammen.

An dieser Stelle wollen wir uns der Frage zuwenden, wie sich ein Multiplexer-Baustein mit Hilfe der elementaren Logikgatter implemen- tieren lässt. Hierzu überführen wir die Wahrheitstabelle des 1-aus-8- Multiplexers in einen booleschen Ausdruck und erhalten das folgende Ergebnis:

y = (s2^s1^s0 ^x1)_(s2 ^s1^s0 ^x2) _ (s2^s1^s0 ^x3)_(s2 ^s1^s0 ^x4) _ (s2^s1^s0 ^x5)_(s2 ^s1^s0 ^x6) _ (s2^s1^s0 ^x7)_(s2 ^s1^s0 ^x8)

Das hieraus resultierende Schaltnetz ist in Abbildung 7.6 dargestellt.

Wie das Strukturbild bereits vermuten lässt, ist der Flächenbedarf großer Multiplexer-Bausteine nicht unerheblich. Implementieren wir die Schaltung, wie hier gezeigt, als zweistufiges Schaltnetz, so benö- tigen wir zur Umsetzung eines 1-aus-n-Multiplexers n UND-Gatter mit jeweils log2n+1 Eingängen. Gehen wir davon aus, dass die Größe ei- nes UND-Gatters proportional mit der Anzahl seiner Eingänge steigt,

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Multiplexer-Implementierung

4

s2 s0 x1

x3 x5 x7 x2 x4 x6 x8

8:1

MUX y

s1

x1

s2 s1 s0 x2

x3 x4 x5 x6 x7 x8

≥1

y

&

&

&

&

&

&

&

&

Abbildung 7.6: Realisierung eines 1-aus-8- Multiplexers mit Hilfe der elementaren Lo- gikgatter

208 7 Standardschaltnetze

s0 x1

x2

2:1

MUX y

s0 s1 x1

x3 x2

x4 4:1

MUX y

s2 s0 x1

x3 x5 x7 x2 x4 x6 x8

8:1

MUX y

s1

s0 y

0 x1

1 x2

s1 s0 y

0 0 x1

0 1 x2

1 0 x3

1 1 x4

s2 s1 s0 y s2 s1 s0 y

0 0 0 x1 1 0 0 x5

0 0 1 x2 1 0 1 x6

0 1 0 x3 1 1 0 x7

0 1 1 x4 1 1 1 x8

Abbildung 7.5: Multiplexer-Bausteine verschiedener Größen

gang y durch. Alle anderen Eingänge werden durch den Multiplexer faktisch vom Rest der Schaltung abgetrennt, so dass die dort anliegen- den Signalwerte für den Ausgangswert keine Rolle spielen. Da mit m Steuerleitungen 2m verschiedene Möglichkeiten unterschieden werden können, entspricht die Anzahl der Eingänge eines Multiplexers in aller Regel einer Zweierpotenz. Abbildung 7.5 fasst die Wahrheitstabellen und Schaltsymbole von Multiplexern verschiedener Größe zusammen.

An dieser Stelle wollen wir uns der Frage zuwenden, wie sich ein Multiplexer-Baustein mit Hilfe der elementaren Logikgatter implemen- tieren lässt. Hierzu überführen wir die Wahrheitstabelle des 1-aus-8- Multiplexers in einen booleschen Ausdruck und erhalten das folgende Ergebnis:

y = (s2^s1^s0 ^x1)_(s2^s1^s0 ^x2) _ (s2^s1^s0 ^x3)_(s2^s1^s0 ^x4) _ (s2^s1^s0 ^x5)_(s2^s1^s0 ^x6) _ (s2^s1^s0 ^x7)_(s2^s1^s0 ^x8)

Das hieraus resultierende Schaltnetz ist in Abbildung 7.6 dargestellt.

Wie das Strukturbild bereits vermuten lässt, ist der Flächenbedarf großer Multiplexer-Bausteine nicht unerheblich. Implementieren wir die Schaltung, wie hier gezeigt, als zweistufiges Schaltnetz, so benö- tigen wir zur Umsetzung eines 1-aus-n-Multiplexers n UND-Gatter mit jeweils log2n+1 Eingängen. Gehen wir davon aus, dass die Größe ei- nes UND-Gatters proportional mit der Anzahl seiner Eingänge steigt,

x1

s2 s1 s0 x2

x3 x4 x5 x6 x7 x8

≥1

y

&

&

&

&

&

&

&

&

Abbildung 7.6:Realisierung eines 1-aus-8- Multiplexers mit Hilfe der elementaren Lo- gikgatter

208 7 Standardschaltnetze

s0 x1

x2

2:1

MUX y

s0 s1 x1

x3 x2

x4 4:1

MUX y

s2 s0 x1

x3 x5 x7 x2 x4 x6 x8

8:1

MUX y

s1

s0 y

0 x1

1 x2

s1 s0 y

0 0 x1

0 1 x2

1 0 x3

1 1 x4

s2 s1 s0 y s2 s1 s0 y

0 0 0 x1 1 0 0 x5

0 0 1 x2 1 0 1 x6

0 1 0 x3 1 1 0 x7

0 1 1 x4 1 1 1 x8

Abbildung 7.5: Multiplexer-Bausteine verschiedener Größen

gang y durch. Alle anderen Eingänge werden durch den Multiplexer faktisch vom Rest der Schaltung abgetrennt, so dass die dort anliegen- den Signalwerte für den Ausgangswert keine Rolle spielen. Da mit m Steuerleitungen 2m verschiedene Möglichkeiten unterschieden werden können, entspricht die Anzahl der Eingänge eines Multiplexers in aller Regel einer Zweierpotenz. Abbildung 7.5 fasst die Wahrheitstabellen und Schaltsymbole von Multiplexern verschiedener Größe zusammen.

An dieser Stelle wollen wir uns der Frage zuwenden, wie sich ein Multiplexer-Baustein mit Hilfe der elementaren Logikgatter implemen- tieren lässt. Hierzu überführen wir die Wahrheitstabelle des 1-aus-8- Multiplexers in einen booleschen Ausdruck und erhalten das folgende Ergebnis:

y = (s2^s1^s0 ^x1)_(s2 ^s1^s0 ^x2) _ (s2^s1^s0 ^x3)_(s2 ^s1^s0 ^x4) _ (s2^s1^s0 ^x5)_(s2 ^s1^s0 ^x6) _ (s2^s1^s0 ^x7)_(s2 ^s1^s0 ^x8)

Das hieraus resultierende Schaltnetz ist in Abbildung 7.6 dargestellt.

Wie das Strukturbild bereits vermuten lässt, ist der Flächenbedarf großer Multiplexer-Bausteine nicht unerheblich. Implementieren wir die Schaltung, wie hier gezeigt, als zweistufiges Schaltnetz, so benö- tigen wir zur Umsetzung eines 1-aus-n-Multiplexers n UND-Gatter mit jeweils log2n+1 Eingängen. Gehen wir davon aus, dass die Größe ei- nes UND-Gatters proportional mit der Anzahl seiner Eingänge steigt,

x1

s2 s1 s0 x2

x3 x4 x5 x6 x7 x8

≥1

y

&

&

&

&

&

&

&

&

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Multiplexer-Anwendungen

§ Steuerung des Datenflusses

5

Analogie: Schienenverkehr Multiplexer entspricht

der Weichensteuerung Hier steuert der Multiplexer,

ob das Ergebnis des Addierers oder des Multiplizierers

weiterverwendet werden soll.

∑

∏ ?

yAddierer

Multiplizierer

s0 x1

x2

Abbildung 7.2:Ein einfaches Rechenwerk.

In Abhängigkeit der Steuerleitung s0 wer- den die Operanden x1 und x2 entweder ad- diert (s0 = 0) oder multipliziert (s0 = 1).

x1 x2

s0

y

Abbildung 7.3: Schienenanalogon. Das Verhalten eines Multiplexers ist dem einer Schienenweiche vergleichbar. In Abhängig- keit des Stellsignals wird genau einer der Eingänge mit dem Ausgang verbunden.

∑

∏

y Addierer

Multiplizierer

s0 x1

x2

2:1 MUX

Abbildung 7.4:Mit Hilfe von Multiplexern werden Datenströme kanalisiert. In Abhän- gigkeit der Steuerleitung wird entweder das obere Eingangssignal (s0 = 0) oder das un- tere Eingangssignal (s0 = 1) auf den Aus- gang durchgeschaltet.

7.2 Multiplexer und Demultiplexer 207

Multiplexer

Multiplexer kommen immer dann zum Einsatz, wenn eine Signalleitung mit einem Wert beschaltet werden soll, der potenziell aus mehreren ver- schiedenen Quellen stammen kann. In anderen Worten: Ein Multiplexer führt Datenpfade gezielt zusammen.

Als Beispiel betrachten wir die in Abbildung 7.2 skizzierte Schaltung.

Das dargestellte Rechenwerk nimmt zwei Zweierkomplementzahlen x

1und x

2entgegen und berechnet in Abhängigkeit der Steuerleitung s

0entweder die Summe oder das Produkt der beiden Operanden. Zu die- sem Zweck hält die Schaltung intern sowohl eine Addier- als auch eine Multipliziereinheit vor, die durch das Auftrennen der Eingangsleitun- gen vollständig parallel arbeiten. In anderen Worten: Zu jedem Zeit- punkt stehen intern sowohl die Summe als auch das Produkt der Ope- randen zur Verfügung.

Damit an den ausgehenden Signalleitungen der korrekte Wert ausge- geben wird, muss das Rechenwerk in Abhängigkeit der Steuerleitung s

0eines der beiden internen Ergebnisse auswählen und nach außen lei- ten. Anders als bei der eingangsseitigen Verzweigung können wir die Datenpfade jedoch nicht einfach physikalisch miteinander verbinden.

Stattdessen benötigen wir eine Schaltkomponente, die in der Lage ist, mehrere Datenquellen als Eingabe entgegenzunehmen und eine davon in Abhängigkeit der Steuersignale auf den Ausgang durchzuschalten.

Genau dies ist die Aufgabe eines Multiplexers. Bildlich gesprochen entspricht das Verhalten eines Multiplexers, wie in Abbildung 7.3 ge- zeigt, exakt dem Funktionsprinzip einer Zugweiche. In Abhängigkeit des Stellsignals wird genau eines der beiden ankommenden Schienen- segmente mit dem nachfolgenden Schienenstrang verbunden.

Abbildung 7.4 zeigt, wie sich die Implementierung des oben skizzier- ten Rechenwerks mit Hilfe eines 1-aus-2-Multiplexers vervollständigen lässt. Ist s

0gleich 0, so wird der Ausgang y mit dem oberen Eingang des Multiplexers und damit mit der Summe aus x

1und x

2beschrieben.

Ist s

0gleich 1, so wird der untere Eingang und damit das Produkt aus x

1und x

2durchgeschaltet.

Neben dem hier eingesetzten 1-aus-2-Multiplexer stehen in der Praxis auch deutlich größere Varianten zur Verfügung. Im allgemeinen Fall verfügt ein 1-aus-n-Multiplexer (n:1 MUX) über die Eingangsleitungen x

1bis x

n, die Steuerleitungen s

0bis s

mund eine einzige Ausgangslei- tung y. In Abhängigkeit der Wertebelegung von s

0bis s

mschaltet der Multiplexer genau eine der Eingangsleitungen x

1bis x

nauf den Aus-

∑

∏ ?

yAddierer

Multiplizierer

s0 x1

x2

Abbildung 7.2: Ein einfaches Rechenwerk.

In Abhängigkeit der Steuerleitung s0 wer- den die Operanden x1 und x2 entweder ad- diert (s0 = 0) oder multipliziert (s0 = 1).

x1 x2

s0

y

Abbildung 7.3: Schienenanalogon. Das Verhalten eines Multiplexers ist dem einer Schienenweiche vergleichbar. In Abhängig- keit des Stellsignals wird genau einer der Eingänge mit dem Ausgang verbunden.

∑

∏

y Addierer

Multiplizierer

s0 x1

x2

2:1 MUX

Abbildung 7.4: Mit Hilfe von Multiplexern werden Datenströme kanalisiert. In Abhän- gigkeit der Steuerleitung wird entweder das obere Eingangssignal (s0 = 0) oder das un- tere Eingangssignal (s0 = 1) auf den Aus- gang durchgeschaltet.

7.2 Multiplexer und Demultiplexer 207

Multiplexer

Multiplexer kommen immer dann zum Einsatz, wenn eine Signalleitung mit einem Wert beschaltet werden soll, der potenziell aus mehreren ver- schiedenen Quellen stammen kann. In anderen Worten: Ein Multiplexer führt Datenpfade gezielt zusammen.

Als Beispiel betrachten wir die in Abbildung 7.2 skizzierte Schaltung.

Das dargestellte Rechenwerk nimmt zwei Zweierkomplementzahlen x

1und x

2entgegen und berechnet in Abhängigkeit der Steuerleitung s

0entweder die Summe oder das Produkt der beiden Operanden. Zu die- sem Zweck hält die Schaltung intern sowohl eine Addier- als auch eine Multipliziereinheit vor, die durch das Auftrennen der Eingangsleitun- gen vollständig parallel arbeiten. In anderen Worten: Zu jedem Zeit- punkt stehen intern sowohl die Summe als auch das Produkt der Ope- randen zur Verfügung.

Damit an den ausgehenden Signalleitungen der korrekte Wert ausge- geben wird, muss das Rechenwerk in Abhängigkeit der Steuerleitung s

0eines der beiden internen Ergebnisse auswählen und nach außen lei- ten. Anders als bei der eingangsseitigen Verzweigung können wir die Datenpfade jedoch nicht einfach physikalisch miteinander verbinden.

Stattdessen benötigen wir eine Schaltkomponente, die in der Lage ist, mehrere Datenquellen als Eingabe entgegenzunehmen und eine davon in Abhängigkeit der Steuersignale auf den Ausgang durchzuschalten.

Genau dies ist die Aufgabe eines Multiplexers. Bildlich gesprochen entspricht das Verhalten eines Multiplexers, wie in Abbildung 7.3 ge- zeigt, exakt dem Funktionsprinzip einer Zugweiche. In Abhängigkeit des Stellsignals wird genau eines der beiden ankommenden Schienen- segmente mit dem nachfolgenden Schienenstrang verbunden.

Abbildung 7.4 zeigt, wie sich die Implementierung des oben skizzier- ten Rechenwerks mit Hilfe eines 1-aus-2-Multiplexers vervollständigen lässt. Ist s

0gleich 0, so wird der Ausgang y mit dem oberen Eingang des Multiplexers und damit mit der Summe aus x

1und x

2beschrieben.

Ist s

0gleich 1, so wird der untere Eingang und damit das Produkt aus x

1und x

2durchgeschaltet.

Neben dem hier eingesetzten 1-aus-2-Multiplexer stehen in der Praxis

auch deutlich größere Varianten zur Verfügung. Im allgemeinen Fall

verfügt ein 1-aus-n-Multiplexer (n:1 MUX) über die Eingangsleitungen

x

1bis x

n, die Steuerleitungen s

0bis s

mund eine einzige Ausgangslei-

tung y. In Abhängigkeit der Wertebelegung von s

0bis s

mschaltet der

Multiplexer genau eine der Eingangsleitungen x

1bis x

nauf den Aus-

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Schaltnetzsynthese mit Multiplexern

6

210 7 Standardschaltnetze

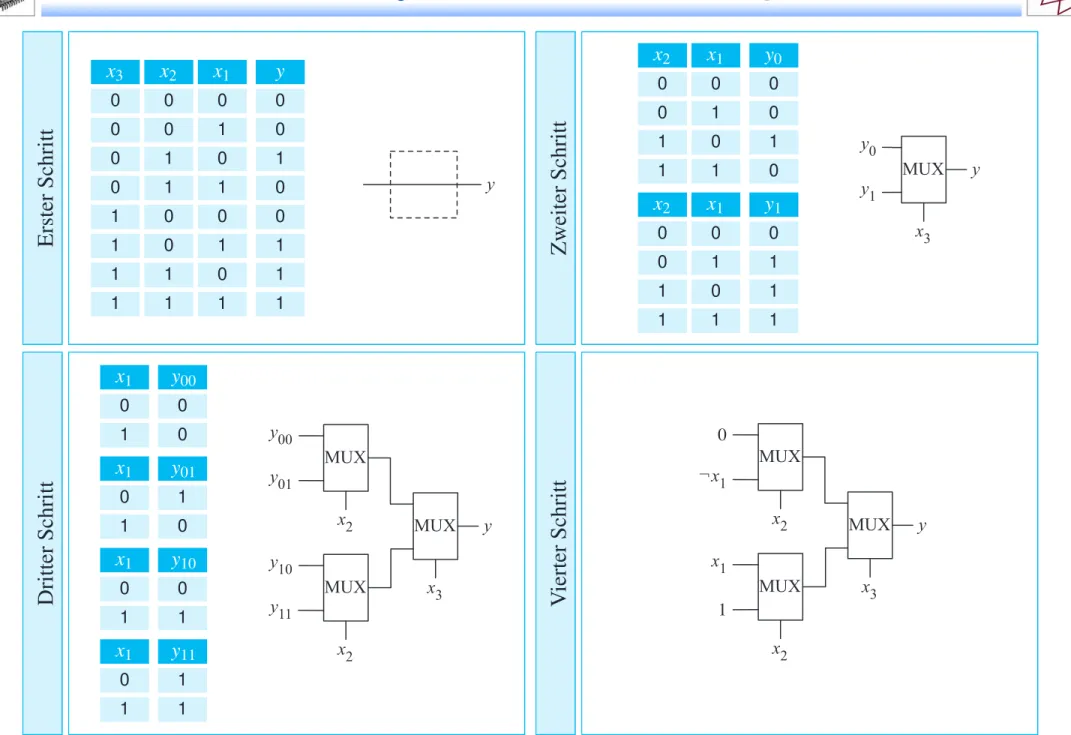

ErsterSchritt

x3 x2 x1 y

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

y

ZweiterSchritt

x2 x1 y0

0 0 0

0 1 0

1 0 1

1 1 0

x2 x1 y1

0 0 0

0 1 1

1 0 1

1 1 1

y0

y1 MUX x3

y

DritterSchritt

x1 y00

0 0

1 0

x1 y01

0 1

1 0

x1 y10

0 0

1 1

x1 y11

0 1

1 1

MUX x2 y00

y01

MUX x2 y10

y11

MUX x3

y

VierterSchritt

MUX x2 0

¬x1

MUX x2 x1

1

MUX x3

y

Abbildung 7.8:Schrittweise Transformation einer beliebigen booleschen Funktion in ein Multiplexer-Schaltnetz

nur erdenkliche boolesche Funktion zu implementieren. Als Ausgangs- punkt verwenden wir die Wahrheitstafeldarstellung einer booleschen Funktion f(x1, . . . ,xn)und setzen diese schrittweise in eine Multiplexer- basierte Schaltung um. Hierzu unterteilen wir die Tabelle jeweils in eine obere und eine untere Hälfte, so dass die Variablenbelegungen der obe- ren Hälfte durch die Bedingung xn = 0 und die Belegungen der unte- ren Hälfte durch die Bedingungxn=1charakterisiert sind. Folgerichtig können wir die boolesche Funktion erzeugen, indem wir die Steuerlei- tung eines 1-aus-2-Multiplexers mit der Variablenxn beschalten und an dem oberen bzw. unteren Eingang des Multiplexers die boolesche Funk- tion der oberen bzw. unteren Hälfte der Wahrheitstafel erzeugen. Durch die wiederholte Zerlegung entsteht ein Schaltnetz für f, das ausschließ- lich aus 1-aus-2-Multiplexern besteht.

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Demultiplexer

7

y1 y2

s0 x

Abbildung 7.10: Genau wie im Falle des Multiplexers ist das Verhalten eines Demul- tiplexers mit dem einer Weiche vergleich- bar. Beide Bausteine unterscheiden sich le- diglich in der Flussrichtung der ein- und ausgehenden Signale.

s2 s1 s0

y1 y2 y3 y4 y5 y6 y7 y8

&

&

&

&

&

&

&

&

x

Abbildung 7.11: Realisierung eines 1-zu- 8-Demultiplexers mit Hilfe der elementaren Logikgatter

7.2 Multiplexer und Demultiplexer 211

x

y1 y2

s0 1:2 DEMUX

s0 s1

y1 y3 y2 y4 1:4

DEMUX x

s

0y

1y

20

x

01 0

x

s

1s

0y

1y

2y

3y

40 0

x

0 0 00 1 0

x

0 01 0 0 0

x

01 1 0 0 0

x

Abbildung 7.9: Demultiplexer-Bausteine verschiedener Größen

Demultiplexer

Bewirken Multiplexer die kontrollierte Zusammenführung von Daten- pfaden, so bewerkstelligen Demultiplexer deren Aufspaltung. Entspre- chend verfügt ein 1-zu-n-Demultiplexer (1:n DEMUX) über eine einzi- ge Eingangsleitung x, die Steuerleitungen s

0bis s

mund n Ausgangslei- tungen y

1, . . . , y

n. In Abhängigkeit der Wertebelegung schaltet der De- multiplexer das Eingangssignal x auf genau eine der Ausgangsleitungen y

1bis y

ndurch und belegt alle anderen Ausgänge mit 0. Abbildung 7.9 zeigt die Wahrheitstabellen und Schaltsymbole eines 1-zu-2- und ei- nes 1-zu-4-Demultiplexers. Da mit n Steuerleitungen 2

nverschiedene Möglichkeiten unterschieden werden können, entspricht die Anzahl der Ausgänge eines typischen Demultiplexers in aller Regel einer Zweier- potenz.

Das Schienenanalogon, das wir zur Veranschaulichung des Multiplexer- Verhaltens herangezogen haben, können wir in direkter Weise auf die Demultiplexer-Schaltung übertragen, indem wir schlicht die Richtung drehen. Wie in Abbildung 7.10 gezeigt, wird der ankommende Schie- nenstrang in Abhängigkeit des Stellsignals mit genau einem der beiden ausgehenden Schienenstränge verbunden.

Aus der Wahrheitstabelle des Demultiplexers lässt sich unmittelbar eine

einstufige Implementierung ableiten. Jedes der Ausgangssignale y

ikann

durch ein einzelnes UND-Gatter erzeugt werden, das neben dem Ein-

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Demultiplexer-Anwendungen (2)

§ Realisierung von logischen Funktionen

§ Der Decoder erzeugt alle 2

nMinterme seiner n Steuerleitungen

§ Ein ODER-Gatter erzeugt die Einsmenge der Funktion

8

c b a y

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

1 DX

c a

≥1

y(a,b,c)

b

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Programmierbare Logikbausteine

9

& ≥1

&

&

&

&

1 1

1 1

x

nx

3x

2x

1≥1

≥1

≥1

≥1

y

my

3y

2y

1UND-Matrix ODER-Matrix

... ...

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Beispiel

10

& ≥1

&

&

&

&

1 1

1 1

x

4x

3x

2x

1≥1

≥1

≥1

≥1

f

4f

3f

2f

1UND-Matrix ODER-Matrix

5.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

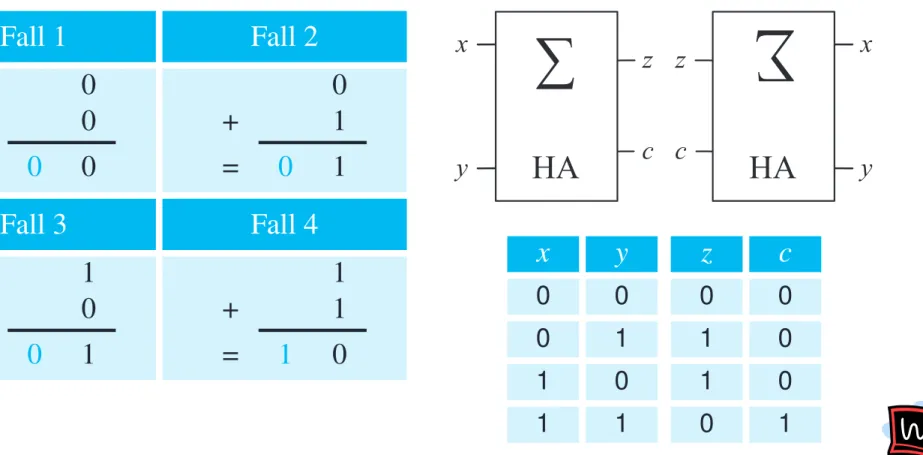

Addierer

§ Halbaddierer

§ Addiert zwei Binärziffern

§ Ergebnis ist der Summenwert und ein Übertrag

§ Es werden 2 Eingänge und zwei Ausgänge benötigt

11

Fall 1 Fall 2

0

+ 0

= 0 0

0

+ 1

= 0 1

Fall 3 Fall 4

1

+ 0

= 0 1

1

+ 1

= 1 0

Tabelle 7.1: Bei der Addition zweier Binär- ziffern müssen wir vier Fälle unterscheiden.

x

y

=

&

z c

∑

HA

x

y

=

&

z c

∑

HA

x y z c

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Abbildung 7.22: Schaltsymbol und Wahr- heitstafel eines Halbaddierers

x

y

=1

&

z c

Abbildung 7.23: Implementierung der Halbaddiererschaltung

218 7 Standardschaltnetze

7.5 Addierer

Die Durchführung arithmetischer Operationen gehört zu den Kernauf- gaben eines jedes Computersystems. In diesem Abschnitt werden wir die verschiedenen Möglichkeiten kennen lernen, wie sich die Additi- on in Form eines Schaltnetzes implementieren lässt. Hierzu werden wir mit dem Halb- und dem Volladdierer zunächst die arithmetischen Ba- siskomponenten einführen und anschließend zeigen, wie sich diese zu komplexen Addierwerken kombinieren lassen. Auch hier werden wir unser besonderes Augenmerk wieder auf die Laufzeit und den Flächen- verbrauch der betreffenden Schaltungen richten.

7.5.1 Halb- und Volladdierer

Der Halbaddierer ist die einfachste arithmetische Basiskomponente und bildet die Addition zweier Binärziffern x und y nach. Da beide Summan- den nur die Werte 0 und 1 annehmen können, müssen wir lediglich die vier in Tabelle 7.1 dargestellten Fälle unterscheiden. Wie die Rechen- beispiele zeigen, setzt sich das Ergebnis der Addition aus dem Summen- bit z und dem Übertragsbit c (Carry-Bit) zusammen, so dass der Halb- addierer neben den beiden Eingangsleitungen x und y über insgesamt zwei Ausgangsleitungen verfügt. Das Schaltsymbol des Halbaddierers ist zusammen mit seiner Wahrheitstafel in Abbildung 7.22 dargestellt.

Die Wahrheitstabelle ergibt sich ohne Umwege aus den binären Additi- onsregeln.

Wie aus der Tabelle hervorgeht, ist das Summenbit genau dann gleich 1, wenn einer der beiden Summanden gleich 1, der andere dagegen gleich 0 ist. Dagegen wird das Übertragsbit nur dann gesetzt, wenn beide Sum- manden gleich 1 sind. Damit erhalten wir für die booleschen Funktionen von z und c das folgende Ergebnis:

z = x

1= x

2c = x

1^ x

2Aus den beiden Gleichungen ergibt sich ohne Umwege die in Abbil- dung 7.23 skizzierte Implementierung, die aus lediglich zwei Logikgat- tern besteht.

Mit Hilfe von Halbaddierern sind wir in der Lage, beliebige Dualziffern zu addieren, für die vollständige Addition mehrziffriger Dualzahlen ist die Funktionalität jedoch noch nicht ausreichend. Als Beispiel betrach- ten wir die Berechnung der Summe 92 + 106, die zusammen mit dem

Fall 1 Fall 2

0

+ 0

= 0 0

0

+ 1

= 0 1

Fall 3 Fall 4

1

+ 0

= 0 1

1

+ 1

= 1 0

Tabelle 7.1: Bei der Addition zweier Binär- ziffern müssen wir vier Fälle unterscheiden.

x

y

=

&

z c

∑

HA

x

y

=

&

z c

∑

HA

x y z c

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Abbildung 7.22: Schaltsymbol und Wahr- heitstafel eines Halbaddierers

x

y

=1

&

z c

Abbildung 7.23: Implementierung der Halbaddiererschaltung