Hochschule Karlsruhe w University of Applied Sciences w Fakultät für Informatik

Prof. Dr. Dirk W. Hoffmann

!

!

Kapitel 3

! Schaltnetze

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Logikgatter

DIN (neu) DIN (alt)

US

DIN (neu) DIN (alt)

US

A N D -V erknüpfung O R-V erknüpfung X O R-V erknüpfung

N O T-V erknüpfung N A N D -V erknüpfung N O R-V erknüpfung

2

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Beispiel

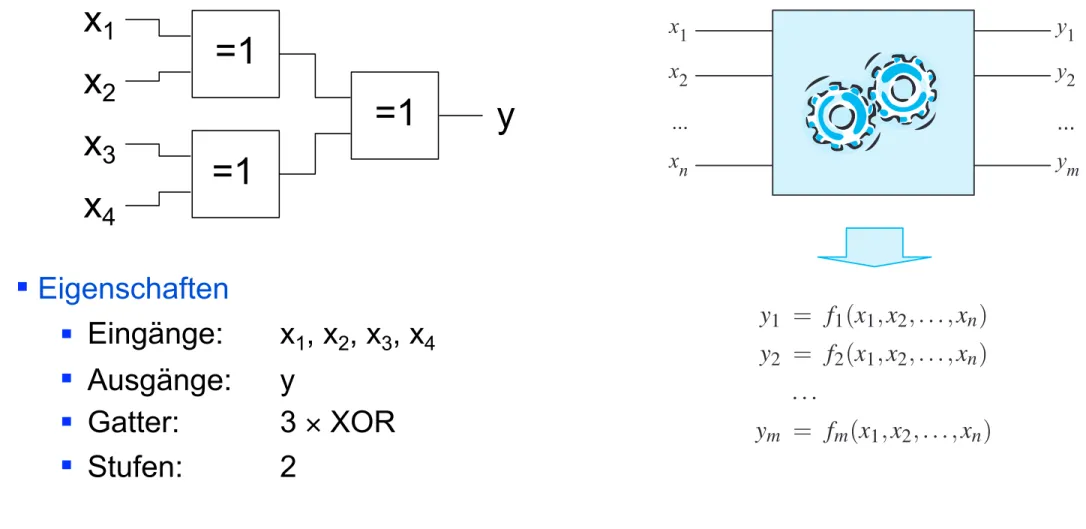

§ Beispiel: Paritätsfunktion

!

!

!

!

!

!

!

§ Eigenschaften

§ Eingänge: x

1, x

2, x

3, x

4§ Ausgänge: y

§ Gatter: 3 × XOR

§ Stufen: 2

§ Allgemeines Schema

=1

=1 x

2y

x

1x

4x

3=1

3

xn x2

y1 y2 x1

ym

... ...

y1 = f1(x1,x2, . . . ,xn) y2 = f2(x1,x2, . . . ,xn)

. . .

ym = fm(x1,x2, . . . ,xn)

Abbildung 5.21: Das Prinzip der funk- tionalen Schaltungsdarstellung. Jedes Aus- gangssignal wird durch eine separate boole- sche Funktion beschrieben.

x1 x2 x3 x4

≥1 y

=1

&

&

Abbildung 5.22: Eine Rekonvergenz ent- steht, indem sich eine Signalleitung ver-

5.3 Formelsynthese 161

5.3 Formelsynthese

In den vorherigen Abschnitten haben wir uns damit befasst, eine boole- sche Funktion ohne große Umwege in ein Schaltnetz zu übersetzen. In diesem Abschnitt wollen wir den umgekehrten Weg beschreiten und uns mit den Möglichkeiten beschäftigen, ein vorgegebenes Schaltnetz in eine boolesche Funktion zu überführen. Auch hier bieten sich uns mehrere Wege, die wir im Folgenden zusammen mit ihren jeweiligen Vor- und Nachteilen kennen lernen werden.

5.3.1 Funktionale Formelsynthese

Für die folgenden Betrachtungen sei ein beliebiges Schaltnetz mit den Eingangssignalen x

1, . . . , x

nund den Ausgangssignalen y

1, . . . , y

mge- geben. Eine funktionale Darstellung des Schaltnetzes erhalten wir, in- dem wir für jedes Ausgangssignal, wie in Abbildung 5.21 gezeigt, ei- ne boolesche Funktion aufstellen, die die Werte der Eingangssignale

x

1, . . . , x

nauf den Wert des entsprechenden Ausgangssignals y

iabbil-

det.

Bei der Übersetzung eines Schaltnetzes in eine boolesche Funktion ma- chen uns vor allem Rekonvergenzen Probleme. Eine Rekonvergenz ent- steht durch die Verzweigung einer Signalleitung am Ausgang eines Gat- ters und die spätere Zusammenführung an den Eingängen eines weite- ren Gatters.

Abbildung 5.22 zeigt ein Beispiel eines rekonvergenten Schaltnetzes.

Die Ausgangsleitung spaltet sich am Ausgang des XOR-Gatters auf und dient beiden UND-Gattern gleichermaßen als Eingangssignal. Die Re- konvergenz entsteht durch die erneute Zusammenführung der beiden Si- gnalwege an den Eingängen des finalen ODER-Gatters. Rekonvergente Schaltungen können wir nicht eins zu eins in einen booleschen Aus- druck überführen. Der Grund hierfür liegt in der Baumstruktur boole- scher Ausdrücke, die sich direkt aus dem rekursiven Konstruktionssche- ma ergibt. Graphentheoretisch betrachtet erzeugt jede Schaltnetzrekon- vergenz eine Maschenstruktur, die sich folgerichtig nicht mehr direkt auf einen booleschen Ausdruck abbilden lässt.

Die einfachste Möglichkeit, die Rekonvergenzproblematik in den Griff

zu bekommen, besteht im vollständigen Ausrollen des Strukturgraphen.

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Beispiel

§ Beispiel: Paritätsfunktion

!

!

!

!

!

!

!

§ Eigenschaften

§ Eingänge: x

1, x

2, x

3, x

4§ Ausgänge: y

§ Gatter: 3 × XOR

§ Stufen: 2

=1

=1 x

2y

x

1x

4x

3=1

x x x x y

0

0 0 0 0 0

1

0 0 0 1 1

2

0 0 1 0 1

3

0 0 1 1 0

4

0 1 0 0 1

5

0 1 0 1 0

6

0 1 1 0 0

7

0 1 1 1 1

8

1 0 0 0 1

9

1 0 0 1 0

10

1 0 1 0 0

11

1 0 1 1 1

12

1 1 0 0 0

13

1 1 0 1 1

14

1 1 1 0 1

15

1 1 1 1 0

4

§ Wahrheitstabelle

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Darstellung in VHDL

§ Beispiel: Paritätsfunktion

with bit_vector'(x4,x3,x2,x1) select

y <= '0' when "0000", '1' when "0001", '1' when "0010", '0' when "0011", '1' when "0100", '0' when "0101", '0' when "0110", '1' when "0111", '1' when "1000", '0' when "1001", '0' when "1010", '1' when "1011", '0' when "1100", '1' when "1101", '1' when "1110", '0' when "1111";

5

x x x x y

0

0 0 0 0 0

1

0 0 0 1 1

2

0 0 1 0 1

3

0 0 1 1 0

4

0 1 0 0 1

5

0 1 0 1 0

6

0 1 1 0 0

7

0 1 1 1 1

8

1 0 0 0 1

9

1 0 0 1 0

10

1 0 1 0 0

11

1 0 1 1 1

12

1 1 0 0 0

13

1 1 0 1 1

14

1 1 1 0 1

15

1 1 1 1 0

§ Wahrheitstabelle

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Optimierte Darstellung in VHDL

§ Beispiel: Paritätsfunktion

architecture demo of fktab is begin

!

!

!

!

!

!

!

!

!

!

!

end demo;

entity fktab is

port(x4,x3,x2,x1:in std_logic;

y:out std_logic);

end;

with bit_vector'(x4,x3,x2,x1) select

y <= '1' when "0001", '1' when "0010", '1' when "0100", '1' when "0111", '1' when "1000", '1' when "1011", '1' when "1101", '1' when "1110", '0' when others;

6

x x x x y

0

0 0 0 0 0

1

0 0 0 1 1

2

0 0 1 0 1

3

0 0 1 1 0

4

0 1 0 0 1

5

0 1 0 1 0

6

0 1 1 0 0

7

0 1 1 1 1

8

1 0 0 0 1

9

1 0 0 1 0

10

1 0 1 0 0

11

1 0 1 1 1

12

1 1 0 0 0

13

1 1 0 1 1

14

1 1 1 0 1

15

1 1 1 1 0

§ Wahrheitstabelle

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Ausnützen von Redundanz

§ Aufgabe

§ Gesucht ist eine Schaltung mit 4 Eingangsleitungen x

1, x

2, x

3, x

4und einer Ausgangsleitung y. Die Schaltung soll für eine BCD-Ziffer bestimmen, ob diese ungerade (y=1) oder gerade ist (y=0).

7

with bit_vector'(x4,x3,x2,x1) select

y <= '0' when "0000",

'1' when "0001",

'0' when "0010",

'1' when "0011",

'0' when "0100",

'1' when "0101",

'0' when "0110",

'1' when "0111",

'0' when "1000",

'1' when "1001",

'-' when others;

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Normalformen (Beispiel)

x x x y

0

0 0 0 0

1

0 0 1 1

2

0 1 0 1

3

0 1 1 0

4

1 0 0 1

5

1 0 1 0

6

1 1 0 0

7

1 1 1 1

8

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Normalformen (Allgemeine Form)

!

§ Allgemeine Form

!

!

!

§ E = Einsmenge von f

§ Jeder Minterm hat die Form (L

n∧ … ∧ L

1) L

i∈ { x

i, ¬ x

i}

§ Jedes L

iheißt ein Literal von f

!

§ Abkürzungen

§ DNF (Disjunktive Normalform)

§ SOP (Sum of products)

!

§ Allgemeine Form

!

!

!

§ N = Nullmenge von f

§ Jeder Maxterm hat die Form (L

n∨ … ∨ L

1) L

i∈ { x

i, ¬ x

i}

§ Jedes L

iheißt ein Literal von f

§

§ Abkürzungen

§ KNF (Konjunktive Normalform)

§ POS (Product of sums)

∨ Minterme

e ∈ E n ∧ ∈ N Maxterm

nGegeben: Boolesche Funktion f(x

n, ..., x

3, x

2, x

1)

Kanonische disjunktive Normalform

9

Kanonische konjunktive Normalform

3.

Technische Informatik I • Hochschule Karlsruhe • Prof. Dr. D. W. Hoffmann

Übergang zur Hardware

y = (x

1∧ ¬x

2∧ ¬x

3) ∨ (¬x

1∧ x

2∧ ¬x

3) ∨ (¬x

1∧ ¬x

2∧ x

3) ∨ (x

1∧ x

2∧ x

3)

Jede Gleichung lässt sich 1:1 in Hardware umsetzen

10